## DESIGN TUTORIAL AND COMPARATIVE ANALYSIS OF PRINTED CIRCUIT BOARD PRODUCTION SOFTWARES FOR MICROCONTROLLER & FPGA-BASED SYSTEMS

by

Ryan Scott Hoover

An thesis submitted to the Faculty of the University of Delaware in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering

Fall 2009

© 2009 Ryan Scott Hoover All Rights Reserved

# DESIGN TUTORIAL AND COMPARATIVE ANALYSIS OF PRINTED CIRCUIT BOARD PRODUCTION SOFTWARES FOR MICROCONTROLLER & FPGA-BASED SYSTEMS

## by

## Ryan Scott Hoover

| Approved: |                                                                   |

|-----------|-------------------------------------------------------------------|

| -P P      | Fouad Kiamilev, Ph.D.                                             |

|           | Professor in charge of thesis on behalf of the Advisory Committee |

| Approved: |                                                                   |

|           | Kenneth E. Barner, Ph.D.                                          |

|           | Chair of the Department of Electrical and Computer Engineering    |

|           |                                                                   |

| Approved: |                                                                   |

|           | Michael J. Chajes, Ph.D.                                          |

|           | Dean of the College of Engineering                                |

|           |                                                                   |

| Approved: |                                                                   |

|           | Debra Hess Norris, M.S.                                           |

|           | Vice Provost for Graduate and Professional Education              |

#### ACKNOWLEDGMENTS

To God, who saves me daily from my own demise and blesses me with the opportunities and people in my life who have allowed me to excel and achieve what would have not otherwise been possible.

To my advisor, Fouad Kiamilev, who is an invaluable resource, guide, mentor, and incredible person. I cannot thank him enough for his dedication to my educational and professional growth as well as all of the members of his research group. His attitude towards problem-solving and failure to accept impossibilities has inspired all who have ever worked with him.

To my parents, without whom my growth as an individual and the opportunities they have worked hard to give me would not have been possible.

To my fiance, Grace, who consistently lifts my spirit and encourages me throughout whatever obstacles I encounter.

To all of the members of CVORG, especially Nick Waite, Rodney McGee, Corey Lange, Rob Haislip, and Furkan Cayci. You have all harbored an exciting and unique environment to work and play that has been invaluable, not to mention awesome! You have all never hesitated to spend time sharing knowledge and time with me, and I could not have accomplished what I did at CVORG without it.

## TABLE OF CONTENTS

| Ll                                 | ST (              | OF TA                                                                | GURES                                                                                                                                                                                                                             | <                |

|------------------------------------|-------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| $\mathbf{C}$                       | hapte             | ${ m er}$                                                            |                                                                                                                                                                                                                                   |                  |

| $egin{array}{c} 1 \ 2 \end{array}$ |                   |                                                                      | UCTION                                                                                                                                                                                                                            |                  |

|                                    | 2.1<br>2.2<br>2.3 | Design                                                               | onent Selection                                                                                                                                                                                                                   | 3                |

| 3                                  | DE                | SIGN                                                                 | PROCESS - CADENCE ALLEGRO 16.2                                                                                                                                                                                                    | 7                |

|                                    | 3.1               | Tutori                                                               | al                                                                                                                                                                                                                                | 7                |

|                                    |                   | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8 | Step 1 - Pad Development25Step 2 - PCB Symbol Development26Step 3 - Part Development34Step 4 - Schematic Development45Step 5 - PCB Layout45Step 6 - PCB Routing55Step 7 - Sending PCB for Fabrication58Step 8 - PCB Fabrication65 | 3<br>4<br>1<br>3 |

|                                    | 3.2               | Rema                                                                 | rks on Cadence Allegro 16.2 Software                                                                                                                                                                                              | 2                |

| 4 |     |                | ESS - ADVAI     |            |          |   |      |      |   |       | 64 |

|---|-----|----------------|-----------------|------------|----------|---|------|------|---|-------|----|

|   | 4.1 | Tutorial       |                 |            |          |   | <br> | <br> | • |       | 64 |

|   |     | 4.1.1 Step 1   | - Part Search   |            |          |   | <br> | <br> | • |       | 64 |

|   |     | -              | - Part Develop  |            |          |   |      |      |   |       | 66 |

|   |     | 4.1.3 Step 3   | - Schematic De  | evelopme   | nt       |   | <br> | <br> |   |       | 73 |

|   |     | -              | - PCB Layout    |            |          |   |      |      |   |       | 74 |

|   |     |                | - PCB Routing   |            |          |   |      |      |   |       | 77 |

|   |     | 4.1.6 Step 6   | - Sending PCE   | 3 for Fabr | rication | 1 | <br> | <br> | • | <br>• | 79 |

|   | 4.2 | Fabricated De  | esign Notes     |            |          |   | <br> | <br> |   |       | 81 |

|   | 4.3 | Remarks on A   | Advanced Circui | its PCB .  | Artist   |   | <br> | <br> |   | <br>• | 81 |

| 5 | CO  | MPARATIVI      | E ANALYSIS      |            |          |   | <br> | <br> |   | <br>• | 82 |

|   | 5.1 | Cadence Alleg  | gro 16.2        |            |          |   | <br> | <br> |   | <br>• | 82 |

|   |     | 5.1.1 Key A    | dvantages       |            |          |   | <br> | <br> |   |       | 82 |

|   |     | *              | isadvantages .  |            |          |   |      |      |   |       |    |

|   | 5.2 | Advanced Cir   | cuits PCB Arti  | st         |          |   | <br> | <br> |   | <br>• | 83 |

|   |     | 5.2.1 Key A    | dvantages       |            |          |   | <br> | <br> |   |       | 84 |

|   |     | ·              | isadvantages .  |            |          |   |      |      |   |       |    |

|   | 5.3 | Conclusions    |                 |            |          |   | <br> | <br> | • |       | 84 |

| 6 | TES | STING          |                 |            |          |   | <br> | <br> | • |       | 86 |

|   | 6.1 | Implementation | on              |            |          |   | <br> | <br> |   |       | 86 |

|   | 6.2 |                |                 |            |          |   |      |      |   |       |    |

|   |     | 6.2.1 DDR 1    | RAM             |            |          |   | <br> | <br> | • |       | 91 |

|   |     | 6.2.2 Small    | Parts           |            |          |   | <br> | <br> | • |       | 91 |

| 7 | CO  | NCLUSIONS      | AND FUTU        | RE WO      | ORK .    |   | <br> | <br> |   |       | 93 |

| R |     | OGRAPHY        |                 |            |          |   |      |      |   |       | 94 |

## LIST OF FIGURES

| 2.1 | Xilinx XC3S500E PQ208 Bank Layout                  | 5  |

|-----|----------------------------------------------------|----|

| 2.2 | Digilent Spartan 3E Starter Kit Board              | 6  |

| 2.3 | SPI Configuration with 3 Daisy-Chained Slaves      | 9  |

| 2.4 | SPI Configuration with 3 Slaves                    | 9  |

| 2.5 | Texas Instruments PTH04070WAH Power Regulator      | 12 |

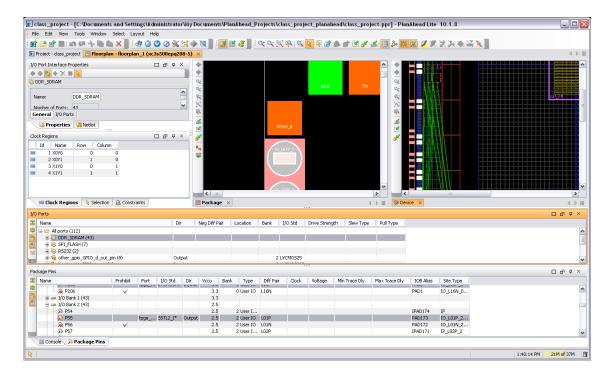

| 2.6 | Xilinx PlanAhead 10.1.8 Pin Planning               | 14 |

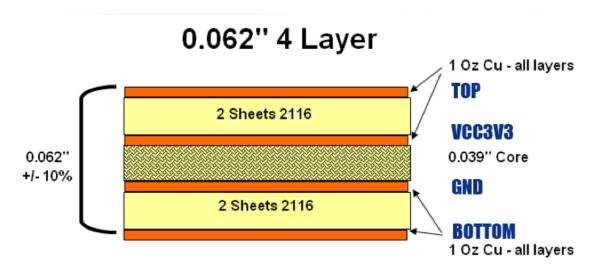

| 2.7 | 0.062" 4-Layer PCB Stack-Up                        | 15 |

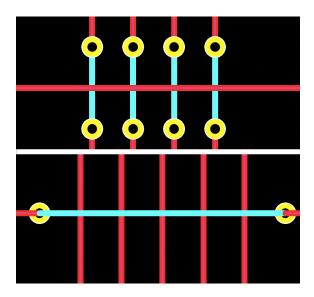

| 2.8 | Simple Design Routing Option Comparison            | 16 |

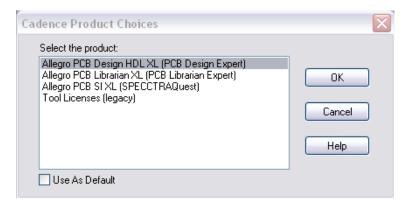

| 3.1 | Cadence Allegro Product Choice Dialogue            | 17 |

| 3.2 | Cadence Allegro New Project Location Dialogue      | 18 |

| 3.3 | Cadence Allegro Project Library Dialogue           | 19 |

| 3.4 | Cadence Allegro Top Level Drawing Dialogue         | 19 |

| 3.5 | Cadence Allegro Project Manager Flow Window        | 20 |

| 3.6 | Cadence Allegro Setup Window Tools Tab             | 21 |

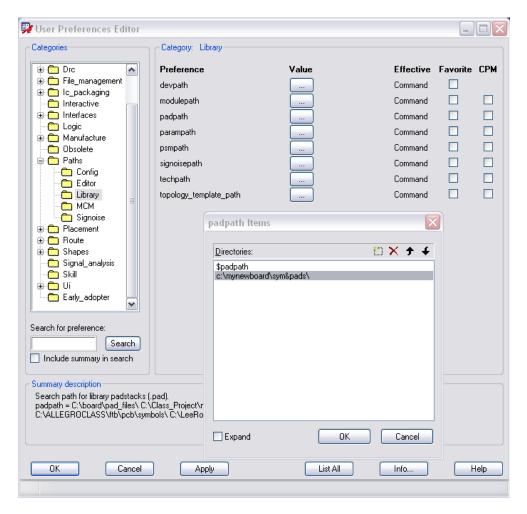

| 3.7 | Cadence Allegro User Preferences Editor            | 22 |

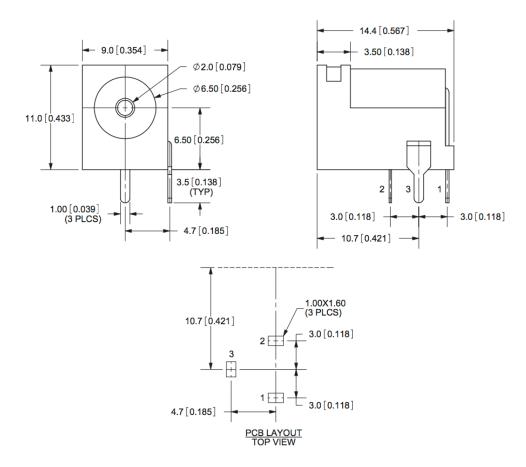

| 3.8 | PJ102-AH Power Connector Socket Datasheet          | 23 |

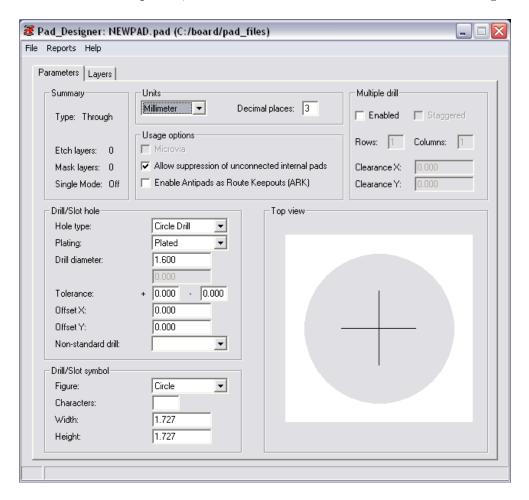

| 3.9 | Pad Stack Editor (Parameters Tab) for PJ102-AH Pad | 24 |

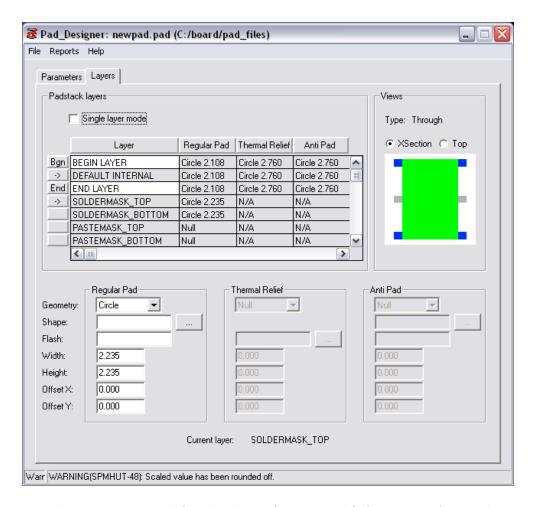

| 3.10 | Pad Stack Editor (Layers 1ab) for PJ102-AH Pad                     | 20 |

|------|--------------------------------------------------------------------|----|

| 3.11 | Fox 50mhz Oscillator Data Sheet                                    | 27 |

| 3.12 | Pad Stack Editor (Layers Tab) for Fox 50mhz Oscillator             | 28 |

| 3.13 | Allegro PCB Editor (Package Symbol) Pin Placement Procedure        | 30 |

| 3.14 | Allegro PCB Editor (Package Symbol) Line Options                   | 31 |

| 3.15 | Allegro PCB Editor (Package Symbol) PJ102-AH Completed Labels      | 33 |

| 3.16 | Allegro PCB Editor (Package Symbol) PJ102-AH Completed Symbol      | 34 |

| 3.17 | Allegro Part Developer - Importer Footprint Selection              | 35 |

| 3.18 | Allegro Part Developer - Importer Pin Assignment                   | 36 |

| 3.19 | Allegro Part Developer - Generate Symbol(s) Dialogue               | 37 |

| 3.20 | Allegro Part Developer - Initial Generated Symbol                  | 38 |

| 3.21 | Allegro Part Developer - Modified Generated Symbol                 | 39 |

| 3.22 | Allegro Part Developer -Part Table File Example for 0805 Resistor  | 40 |

| 3.23 | Allegro Design Entry HDL - Note Entry Window                       | 42 |

| 3.24 | Allegro Design Entry HDL - Page Labels                             | 42 |

| 3.25 | Allegro Design Entry HDL - Component Browser Part Details Tab      | 43 |

| 3.26 | Allegro Design Entry HDL - Example of Simple Schematic Connections | 44 |

| 3.27 | Allegro Design Entry HDL - Example of Bus Tapping                  | 45 |

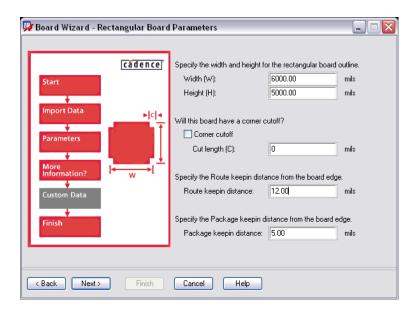

| 3.28 | Allegro PCB Editor - Board Wizard General Parameters               | 47 |

| 3.29 | Allegro PCB Editor - Board Wizard Etch Cross-Section Details       | 48 |

| 3.30 | Allegro PCB Editor - Board Wizard Rectangular Board Parameters | 49 |

|------|----------------------------------------------------------------|----|

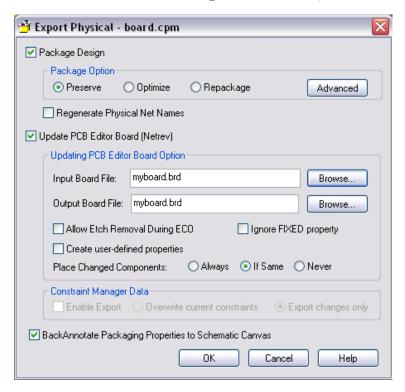

| 3.31 | Allegro Design Sync                                            | 50 |

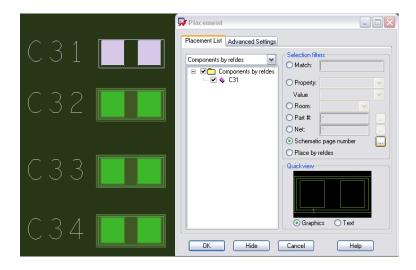

| 3.32 | Allegro PCB Editor - Component Placement                       | 51 |

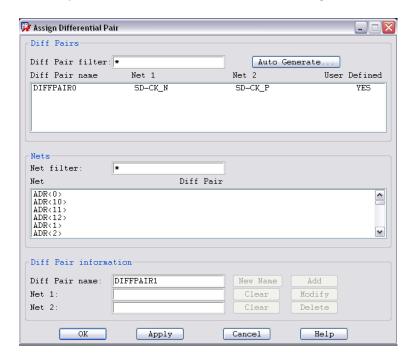

| 3.33 | Allegro PCB Editor - Differential Pair Identification          | 52 |

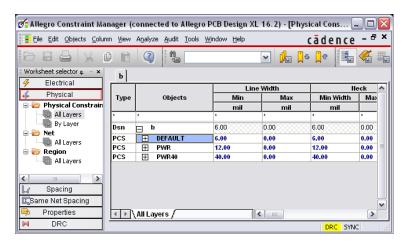

| 3.34 | Allegro PCB Editor - Constraint Manager                        | 53 |

| 3.35 | Allegro PCB Editor - Dynamic Copper Rectangle Options Panel    | 55 |

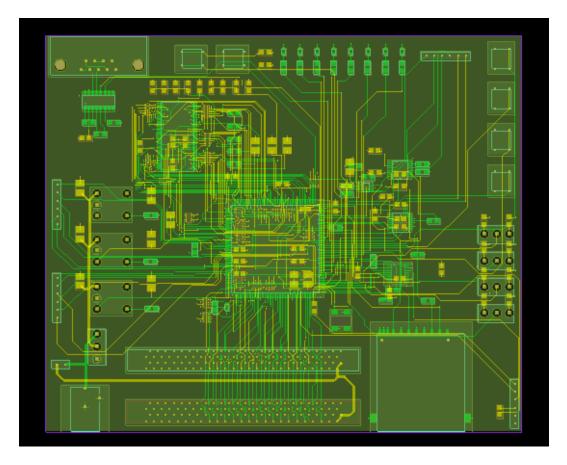

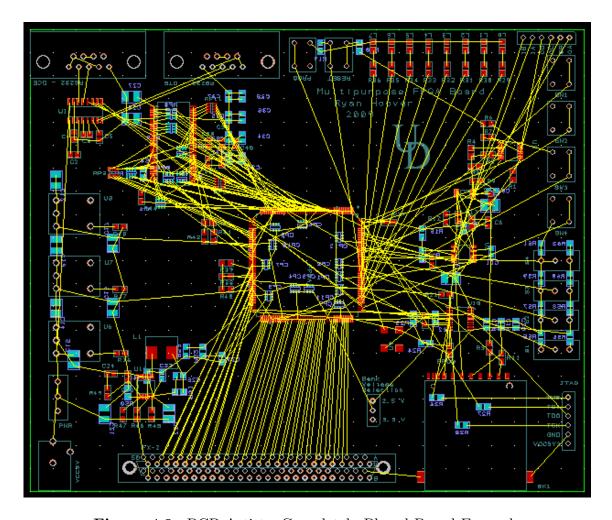

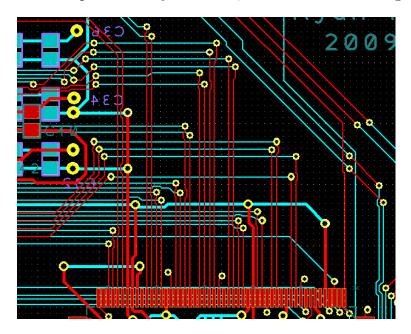

| 3.36 | Allegro PCB Editor - Automatically Routed Board Example        | 56 |

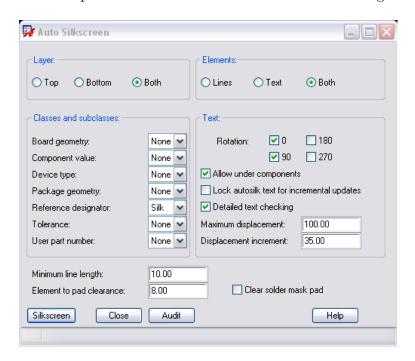

| 3.37 | Allegro PCB Editor - Auto Silkscreen Generator                 | 57 |

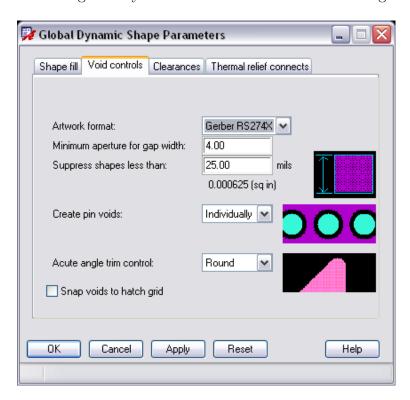

| 3.38 | Allegro PCB Editor - Global Dynamic Shape Parameters           | 58 |

| 3.39 | Allegro PCB Editor - Artwork General Parameters                | 59 |

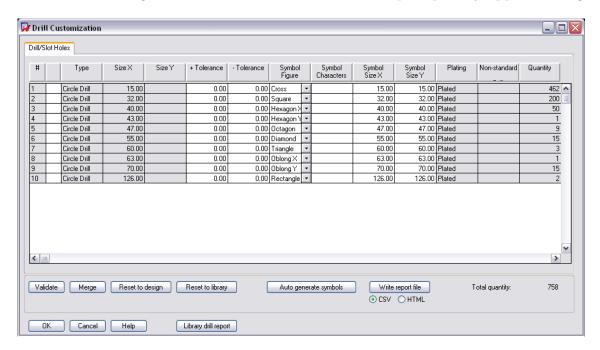

| 3.40 | Allegro PCB Editor - Drill Customization                       | 61 |

| 4.1  | PCB Artist - Online Component Library Search Form              | 65 |

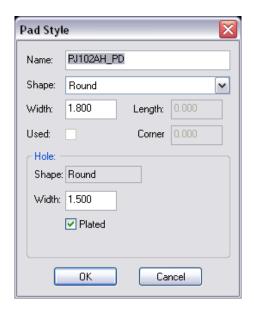

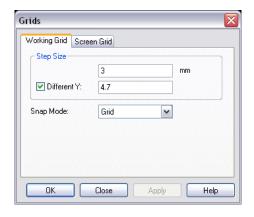

| 4.2  | PCB Artist - Pad Style Dialogue Box for PJ102-AH Pad           | 67 |

| 4.3  | PCB Artist - Pad Grid Settings Window                          | 68 |

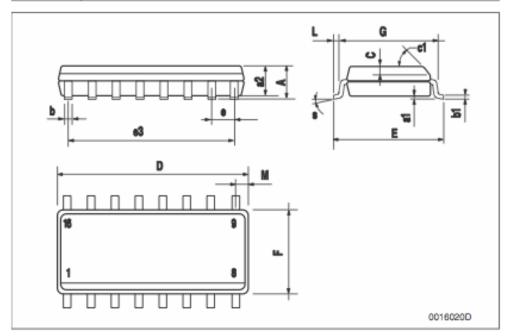

| 4.4  | STMicroelectronics ST3232CDR Package Dimensions                | 70 |

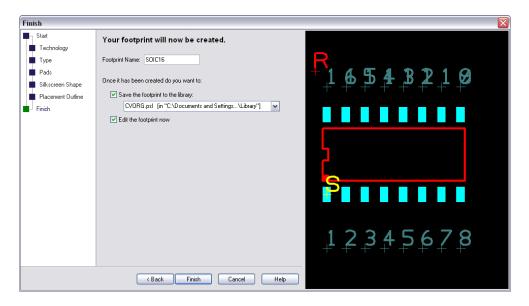

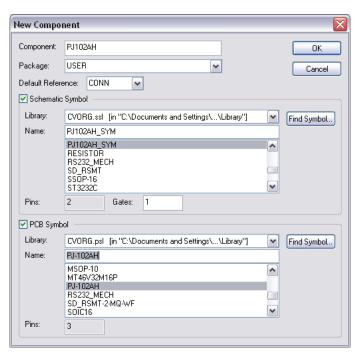

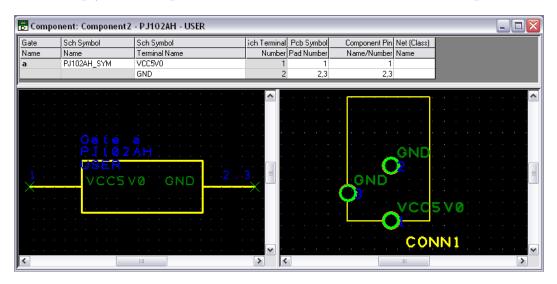

| 4.5  | PCB Artist - Symbol Wizard Finish Prompt                       | 71 |

| 4.6  | PCB Artist - New Component Wizard                              | 72 |

| 4.7  | PCB Artist - Complete Part - PJ102-AH                          | 73 |

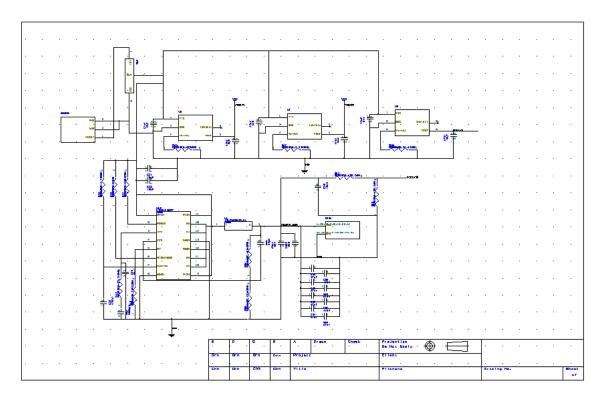

| 4.8  | PCB Artist - Complete Schematic Example                        | 75 |

| 4.9  | PCB Artist - Completely Placed Board Example                   | 77 |

| 4.10 | PCB Artist - Horizontal/Vertical Routing Example               | 78 |

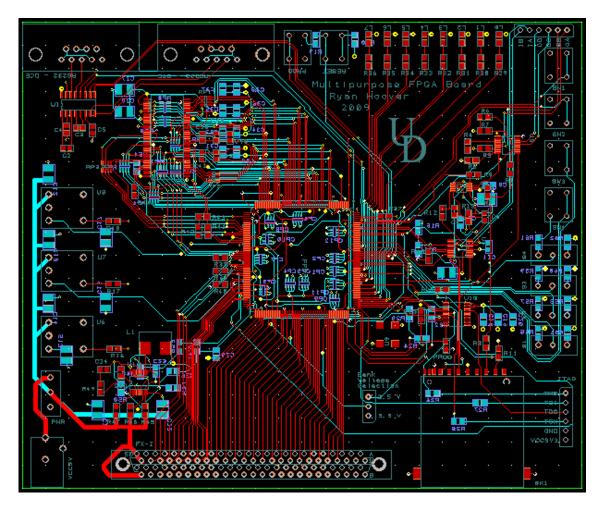

| 4.11 | PCB Artist - Complete Routed Board Example              | 80 |

|------|---------------------------------------------------------|----|

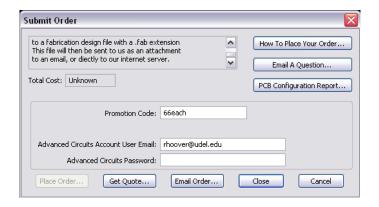

| 4.12 | PCB Artist - Order Submission Form                      | 81 |

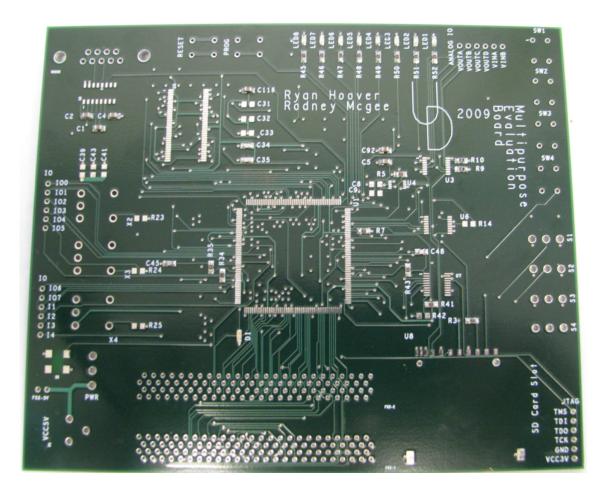

| 6.1  | Cadence Early Design With Only Small SMT Parts Soldered | 87 |

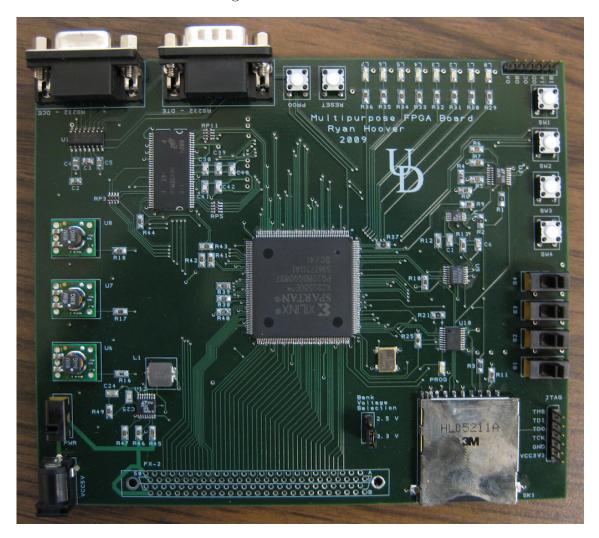

| 6.2  | PCB Artist Board Mostly Assembled                       | 88 |

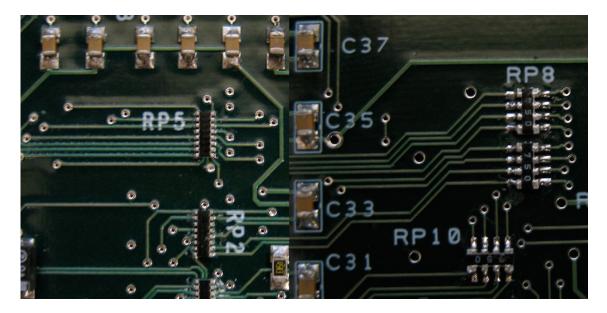

| 6.3  | 8-Array (Left) VS 4-Array (Right) Size Comparison       | 92 |

## LIST OF TABLES

| 2.1 | Basic Board Requirements                        |

|-----|-------------------------------------------------|

| 2.2 | Secure Digital Pinouts for 3 Modes of Operation |

| 2.3 | Possible Component Requirements                 |

| 2.4 | www.66each.com PCB Specifications               |

| 3.1 | Design Files Needed for Successful Fabrication  |

| 5.1 | Cadence Allegro Design Suite 16.2 Components    |

#### ABSTRACT

Printed Circuit Board design and implementation is a research topic most any company or group manufacturing electronic devices must address. There are issues in every aspect of design, ranging from schematics to pad stacks to routing. An error in any one of these steps propagates through the remaining steps. There are many approaches and software packages for moving a design from schematics to a physical PCB. However, software packages can range from being free to costing thousands.

This thesis describes the design process from start to finish of a multi-purpose FPGA-based printed circuit board in two competing software packages. It will detail issues encountered along the way, and how these issues were resolved. Commercially available products will be used throughout the process, including the Xilinx Spartan 3E FPGA. The differing design processes in the software packages Cadence Allegro Design Entry HDL and Advanced Circuits PCB Artist will be detailed and explored in order to determine which characteristics of each package suites various types of hardware design.

The goal of this project is to create a "reference manual" for students to use as a guide in choosing a software package and working through the PCB design process at the University of Delaware's Electrical and Computer Engineering Department. These two software packages are available to all students in the department to learn and design printed circuit boards.

#### Chapter 1

#### INTRODUCTION

Printed circuit boards have been around since the 1940s. In fact, the first one was made in 1934, and they were used extensively for rugged radio designs in World War II during the 1940s. However, it wasn't until after the war that the US released the invention for commercial use. In fact, they did not become commonplace in electronic devices until the 1950s, after the US Army invented a much more streamlined method of assembly. Since then, printed circuit boards have become perhaps the most essential part to the devices that millions of people use every day. Since their invention, the process of designing a printed circuit board has become much less tedious, and there are many ways to make a finished product.

This thesis will describe two modern ways of doing PCB design with computers, and their advantages and drawbacks. It will describe the complete printed circuit board creation process, from component selection to finished product. This example will be a multipurpose field programmable gate array based board, meaning this will be the controlling component on this circuit board. A field programmable gate array, or FPGA, is an integrated circuit that is designed to include a vast array of reconfigurable hardware. This means that the user can apply different hardware configurations when necessary. While an application-specific integrated circuit is locked in once fabricated, an FPGA can be reprogrammed to implement whatever logical circuit the user wishes. This has obvious advantages, and allows for the rapid prototyping of new devices, as well as very flexible design processes.

Modern FPGAs are even capable of implementing microprocessors onboard, along with an application-specific circuit all on the same chip. This allows developers to run software alongside a hardware design created in a hardware description language such as VHDL or Verilog, and reconfigure the entire design on the fly. Tools such as the Xilinx Embedded Design Kit allow the designer to create systems with communication between hardware designs in a hardware description language and software written in a high-level computing language. This powerful combination can even be endowed with the power and functionality of an operating system, namely Linux, opening the door to a world of power that would not be otherwise possible. It is this powerful functionality that makes FPGAs perfect for this general-purpose board.

The structure of this thesis will begin with a description in Chapter 2 of the specific requirements for this particular printed circuit board. This includes walking through the component selection process, and noting design considerations and layout restrictions along the way. Next, in Chapter 3, the development process using Cadence Allegro 16.2 will be described in detail all the way to sending the PCB off for fabrication at our choice of foundry, Advanced Circuits. In the following chapter, the same process is described using another design package authored by the foundry, Advanced Circuits, called PCB Artist. Then in Chapter 5, the processes in the competing packages will be compared in detail, discussing application-specific advantages of each. The testing procedure will be described in Chapter 6, including the successes and failures of the various components. Finally, the conclusions that can be drawn from this work will be described, as well as possible future plans for this work.

#### Chapter 2

### **BOARD REQUIREMENTS**

When beginning a printed circuit board project, the most important thing to do is to get a list of all the requirements, components, etc. that the final product will need to possess. The list below is the list of preliminary components that were required for this particular application, which is a custom controller for a custom testing platform.

Table 2.1: Basic Board Requirements

| Required Component        | Details                                         |

|---------------------------|-------------------------------------------------|

| FPGA                      | approximately 150 inputs/outputs; Linux capable |

| Clock                     | 50mhz speed                                     |

| PROM                      | for program on power-up w/ JTAG interface       |

| DDR-SDRAM                 | about 64MB of memory                            |

| Serial Port               | DTE (DCE optional)                              |

| SD Card Slot              | can use SPI interface (low volume of data)      |

| Analog-Digital Conversion | atleast 2 analog inputs                         |

| Digital-Analog Conversion | atleast 2 analog outputs                        |

| FX-2 Connector            | atleast 20 digital outputs                      |

| Switches/Buttons/LEDs     | assorted I/O for physical interaction with user |

#### 2.1 Component Selection

Component selection is perhaps one of the most important steps in the printed circuit board creation process. If a mistake or error is made in this step, it can result in hours of lost work or worse yet, a useless fabricated board. Therefore, one must be sure to choose components carefully. The primary thing to look for in a part is

its ability to satisfy or exceed the requirements originally established. Obviously, if a part does not accomplish what it is required to, the board will be useless in the application it was intended for. The second thing to consider when selecting parts is its size. Small sized parts are great when it is necessary to fit many parts onto a small board. However, this may not be ideal when considering how the board is to be assembled. For example, the common 0402 sized part is very small, and can be soldered by a human. It is, however, difficult to solder by hand, and will take much longer than a larger sized part, such as an 0805 if the space is available. Another very important factor to consider when selecting components is the voltage and current they will require. It is desirable to use components throughout a design that have the same voltage, and to design a power supply system that is capable of providing not only the voltages required by the components, but also enough current for normal operation as well as instantaneous power operations.

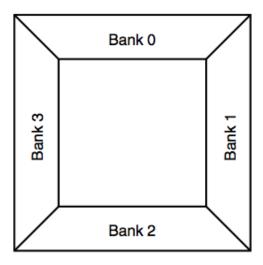

Keeping these things in mind, the components were chosen. The most important component, the FPGA, is a Xilinx Spartan XC3S500E chip. This particular chip comes in several different sizes and packages. Some of these have more input/output pins than others, mostly because of size constraints. For the size and scale of this particular process, the PQ208 package was chosen. This chip is 28mm by 28mm, and has 208 pins with a 0.5mm pitch. These specifications are suitable for this project because they allow for an acceptable number of input/outputs while maintaining the ability to be soldered by hand. This particular model contains 500,000 gates, 158 input/outputs (65 differential), 1164 logic blocks, and a 2.7ns delay time. The FPGA itself requires a 1.2V and 2.5V supply. The device is also capable of input and output using the LVCMOS, LVTTL, HSTL, and SSTL single-ended signal standards. The input/ouputs on the FPGA are divided into banks, with 4 banks total. Each bank is powered individually, and must be configured to operate at the voltage it is powered at. The banks are organized physically as

shown in figure 2.1 below. It is important to note the number of inputs and outputs

Figure 2.1: Xilinx XC3S500E PQ208 Bank Layout

available on each bank, and plan the connections to other components accordingly. If this is not done carefully, the designer may end up with usable inputs and outputs which are tied to an undesirable voltage. Furthermore, care must be given to physical arrangement of components such that locality is preserved between banks and their respective connections to components.

Another important requirement for this design is the PROM chip. Without one, the FPGA will need to be programmed every time the power is cycled. There are many different kinds of PROM chips. PROM stands for Programmable Read-Only Memory. Because this type of memory is meant to be read quickly on a regular basis, writes typically take much longer than reads. PROM chips exist for many different types of devices, not just FPGAs. Fortunately, Xilinx makes a PROM chip that is designed to work specifically with many members of the Xilinx FPGA line. For this application, the Xilinx XCF04S was chosen. The XCF04S features programability through the JTAG interface. This will allow us to arrange the PROM and the FPGA in a JTAG chain such that we will be able to program the devices independently through a single interface. Another important consideration is that

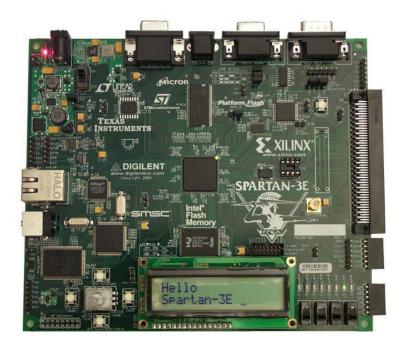

the XCF04S comes in a package which is easily hand-soldered, and takes a standard 3.3 volt supply. This particular device also happens to be of relatively low cost when compared to other available options. Another reason to use this particular device is that it is already used in combination with the XC3S500E on a commercially available board made by Digilent called the Spartan-3E starter kit board. Looking at devices which contain some of the components you wish to use is helpful because it is working proof that those components work well together. There are several other components on this board which meet the requirements listed above. The board is shown in figure 2.2 below.

Figure 2.2: Digilent Spartan 3E Starter Kit Board

Choosing an external clock is important when working with FPGA-based devices. Without a clock, an FPGA is still very useful for simple hardware designs, but in any system that has communication or performs computation, a clock is essential. When choosing a clock speed, it is usually favorable to choose close to the fastest recommended clock speed that the FPGA is capable of. This is because

while the clock can be divided or slowed down to the desired speed, it cannot be made to change state faster. It is also important to note that our FPGA is able to handle modifications to the clock because it has a Digital Clock Manager (DCM). A designer must be sure to carefully check the recommended operating conditions for the DCM, and chose a clock accordingly. Fortunately, in this case, Digilent has selected a clock for the starter board that will work very nicely in this system. It provides a 50 Mhz clock signal, and uses a standard 3.3 volt supply. It also uses a simple footprint, and therefore is a suitable candidate for this application.

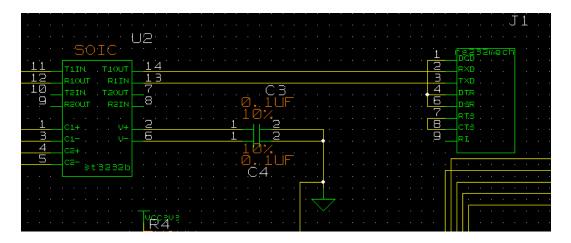

The next component that needs to be selected is a serial port. The choice of the physical serial connector is relatively easy, as there are very few choices. For this application, a standard female DB-9 connector will work just fine. These are easy to search for and find with many options, although most will have the same footprint, as it is a standard common part. However, the pins of the serial (RS-232) connector cannot be directly connected to the FPGA. The FPGA is incapable of reading and providing the correct type of signals for serial communications. Therefore, we must add another component to fulfill the requirement that this board have serial communication. Fortunately, there are many integrated circuits available to provide this functionality made specifically for serial communications. A quick search on a popular site like Digikey or Newark Electronics will yield a vast selection of components that would meet the requirements. However, since this type of component is also on the Spartan-3E starter board, it is safer and easier to use the same component as long as additional functionality is not required. In this case, that component is the ST3232CDR, a transceiver chip which can be powered with 3.3 volt supply and comes in a standard SOIC-16 package. Standard package sizes are favorable because the design footprints for these sizes are often included with printed circuit board design software, and can be reused for other IC chips. The ST3232CDR can run at data rates of up to 250 kbps and still keep RS-232 output levels, which is much

faster than is needed for this design.

Selecting the Secure Digital card socket is trivial, however deciding how it will interact with the FPGA is not. The Secure Digital standard provides operation in three modes, outlined in the table below: These modes of operation all provide

**Table 2.2:** Secure Digital Pinouts for 3 Modes of Operation

| Pin | SD 4-Bit Mode              | SD 1-Bit Mode        | SPI Mode             |

|-----|----------------------------|----------------------|----------------------|

| 1   | DAT[3] - Data Line 3       | N/C - Not Used       | CS - Control Signal  |

| 2   | CMD - Command Line         | CMD - Command Line   | DI - Data Input      |

| 3   | VSS1 - Ground              | VSS1 - Ground        | VSS1 - Ground        |

| 4   | VDD - Supply Voltage       | VDD - Supply Voltage | VDD - Supply Voltage |

| 5   | CLK - Clock                | CLK - Clock          | SCLK - Clock         |

| 6   | VSS2 - Ground              | VSS2 - Ground        | VSS2 - Ground        |

| 7   | DAT[0] - Data Line 0       | DATA - Data Line     | DOUT - Data Output   |

| 8   | DAT[1] - Data Line $1/Int$ | IRQ - Interrupt      | IRQ - Interrupt      |

| 9   | DAT[2] - Data Line $2/RW$  | RW - Read Wait       | NC - Not Used        |

certain advantages and disadvantages. An important consideration to note is that many analog-to-digital/digital-to-analog converters also operate using the SPI standard. In fact, the analog-to-digital/digital-to-analog converters on the Spartan 3E starter kit board use the SPI standard. So, if we decided to use SPI mode for the SD card, the only signal that is unique to the SD card would be the CS, or control signal. This means less FPGA pins are used. In contrast, SPI is the slowest standard of the three, and is not suitable for transferring large amounts of data. Therefore, if the SD card is going to be used for sustained data transfer, SPI would not be a suitable operation mode. However, in this case, the requirements permit for the use of SPI mode, as there will be a low volume of data traffic to/from the SD card. In addition, this project demands as many digital input/outputs as possible, and the use of SPI mode allows for more allocation of general purpose input/output pins (GPIO).

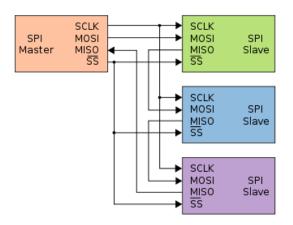

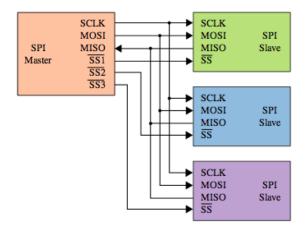

Using SPI mode with more than one device, in our case the SD Card and

the analog-digital conversion ICs, can be configured one of two ways. In the first scenario, all SPI devices share a CLK signal, and SS (or CS - Control Signal), and Master In Slave Out (MISO) and Master Out Slave In (MOSI) are configured in a daisy-chain, as shown in the figure below. The second configuration also has a shared

Figure 2.3: SPI Configuration with 3 Daisy-Chained Slaves

CLK signal. However, there is an independent SS (or CS - Control Signal) for each slave device. There is no daisy-chaining the MOSI and MISO signals. Instead, they are shared signals, as shown in the figure below. Since the ability to implement SPI

Figure 2.4: SPI Configuration with 3 Slaves

in the daisy-chained configuration requires device-compatibility, and also increases

the complexity of the system, the logical choice is to arrange the devices in a typical SPI configuration.

For the last several components that still need to be selected, it is prudent to draw knowledge again from the Spartan 3E starter board. The digital-analog converter on the starter board is a Linear LTC2624 chip, a 16-pin, 12-bit precision digital to analog converter. It can handle a 3.3V supply voltage, and can be operated at clock speeds of up to 50 megahertz. This chip will suit the requirements of this board easily, although it should be noted that there are other models of this chip with up to 16-bit precision. Likewise, the analog-digital converter used on the starter board is a Linear LTC1407 chip, a 10-pin, 12-bit precision analog to digital converter. It also handles a 3.3V supply voltage, and can sample input between -1.25V and 1.25V. For this reason, an amplifier IC is also needed to apply gain (negative or positive) to the incoming signals. The chip used on the starter board is another Linear chip, the LTC6912. This chip has 2 channels with independent gain control. It also uses an SPI interface, and takes a 3.3V supply voltage. These three chips provide four analog out channels and two analog input channels, which meet the specified requirements. The user interface components on the starter board are simple, and are large enough that a user can easily interact with them. The LEDs are bright, and about the same size as the other 0805 resisters and capacitors that will be chosen. Therefore, for this design, the same push buttons, and slider switches will be used. These are part numbers EVQ-PAE04M and 10SP001, respectively. This design will also use a similar FX-2 connector to connect to GPIO. While the starter board has a right-angled socket, this design will use a vertical socket to make it easier to connect to. The part number is FX2CA2-100S-1.27DSA, made by Hirose.

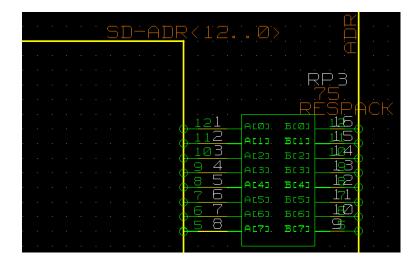

The last required component is a DDR SDRAM chip. There are many things to consider when selecting memory. Data bus width, instruction width, placement requirements, power consumption, and size are only a few. Fortunately, the requirements for this project are simply that DDR SDRAM storage is present. Because the FPGA will be clocked at 50 megahertz, it will be under-clocking the DDR SDRAM to begin with. It is known that the DDR-SDRAM on the starter board works well, so this selection will also mirror the starter board. This chip is the MT46V32M16P-6T, a 66-pin package that has a data width of 16 bits (also capable of running with 8 bits), and is capable of running at speeds of up to 167 megahertz. There are many considerations and restrictions to consider when using DDR SDRAM that will be covered later in this thesis. As will be described in further detail later, Xilinx provides a tool called Memory Interface Generator (MIG) that will provide the correct pin configuration for the specific Xilinx FPGA that is being used. The tool will also provide information on compatibility between specific DDR SDRAM chips and the FPGA that is being used.

Once all of the major component requirements have been selected, it's important to look at the requirements of the components. Each component may require any of the additional components listed in the table below. It's important to care-

**Table 2.3:** Possible Component Requirements

| Possible Requirement          | Example                           |

|-------------------------------|-----------------------------------|

| Specific Power Supply Voltage | 2.5V, 3.3V                        |

| Maximum Current/Power Draw    | $0.7 \text{mA}, 3.5 \mu \text{A}$ |

| Bypass Capacitors             | $10\mu\mathrm{F},47\mathrm{nF}$   |

| Misc Capacitors               | 220nF, etc                        |

| Misc Resistors                | $1k\Omega$ , $100\Omega$          |

| Misc Inductors                | $6.8 \mu H, 10 \mu H$             |

| Differential Pair             | + and $-$ signals                 |

fully check the data sheets of the components that were selected to identify any additional parts that might be required. In the case of this project, there are many resistors, capacitors, and bypass capacitors. Most of the resistors and capacitors come in standard 0805 size. This is preferable because 0805 parts are easily hand

solderable, but are quite small and make good use of available space. Some of the required capacitors, however, do not come in 0805 packages, primarily because of size limitations. Fortunately, the remaining capacitor parts come in several other standard packages. For this project, it is most convenient to stick with surface mount parts, and tantalum capacitors offer that advantage. Therefore, the remaining capacitors are selected in 3528-21 standard size.

Now that all of the components have been selected, power and routing requirements must be taken into account. We have 4 separate voltages that are required, 1.2V, 1.25V, 2.5V, and 3.3V. There are several ways to provide these voltages. It should also be noted that it is recommended the DDR SDRAM have its own separate power supply, meaning separate 2.5V and 1.25V supplies. The chip used on the starter board to supply these voltages is a standard package and is produced by Linear, the same company that makes the ADC/DAC chips, so this chip will work nicely for this design. However, the chip used on the starter board to supply 1.2V, 2.5V, and 3.3V to the FPGA is a special Texas Instruments chip that must be baked on the board, and cannot be hand-soldered. Therefore, this makes it an undesirable choice for this project. There are not many chips on the market that will provide all three of these voltages in a single package. However, there are many regulators available that have adjustable output based on a resistor value. This lead the search to the PTH04070WAH, a Texas Instruments regulator that takes a 5V supply, and is capable of producing each of the three required voltages. A set resister is used to control the output voltage. This part comes in a 5 pin through-hole package, and will work nicely in this design. It is pictured below. Of course, since three voltages

Figure 2.5: Texas Instruments PTH04070WAH Power Regulator

are required, three voltage regulators must be used.

#### 2.2 Design Considerations

Once all of the parts have been selected, there are factors which a designer should take into consideration before beginning the design process. The most important of these, especially when dealing with micro controllers or FPGAs is the pin mapping. This is especially important because once a PCB is fabricated, it is very difficult to re-route connections which are incompatible with the pins they are attached to. On FPGAs and micro controllers, pins have different capabilities and input/output standards, so its very important to make sure that when selecting pins for peripherals, they can support the needed input/output standards. It's also important to conserve the available resources. For instance, a standard practice is pin sharing when there aren't enough pins for all the peripherals. Of course this means that only one of the peripherals with shared pins can be effectively used at once without using multiplexing, and the pins of both peripherals must share a common input/output standard. Another way to save pin resources are to operate some peripherals with a smaller data bus. For instance, the SD card is capable of operating in both 4-bit and 1-bit data mode. If the SD card is not being used for sustained, high-volume data transfer, 1-bit mode is quite sufficient, and 3 more pins are available for other peripherals. For some devices, such as the Xilinx line of FPGAs, there is software available from the manufacturer to aid in the placement of peripheral pins. In Xilinx's PlanAhead software package, there is a pin planning tool that even has the ability to take a UCF file from their EDK, ISE tools to help in pin placement planning. This software tool is pictured below in Figure 2.6. The use of these hardware planning tools can help to eliminate errors and identify issues which may have been ordinarily overlooked.

In addition to pin planning, physical board constraints must be decided. Is this device going to be embedded into a system? How much space is available? How

Figure 2.6: Xilinx PlanAhead 10.1.8 Pin Planning

many layers should the PCB contain? How much will it cost, and what can be done to make the cost per board as low as possible? These are all important questions to consider before beginning the design process. The further into the design process, the more difficult to make changes to constraints like PCB size/shape, and number of layers. It is also important to identify all design constraints such as differential pairs and line length limitations, such as those involved with DDR SDRAM which prevent skew and preserve signal integrity. Logging all of these constraints, and then checking them individually before sending out the design for fabrication can save tremendous amounts of time and money in the long run. For this particular design, it was decided that Advanced Circuits (\$)66each.com process would be used. This requires that the design be limited to specifications listed below. It is for this reason that this board will be 6" by 5", and 4 layers. The two internal layers will be power planes. Since the ground signal is used all over the board, it is logical to make this

Table 2.4: www.66each.com PCB Specifications

| Table 2.11 WWW.occom.com 1 CB Specifications            |

|---------------------------------------------------------|

| Design Requirement                                      |

| 4-Layers, FR-4, 0.062", 1 oz cu Plate                   |

| Lead Free Solder Finish                                 |

| Minimum 0.006" Line Spacing                             |

| Minimum 0.015" Hole Size                                |

| All Holes Plated                                        |

| Green LPI (Liquid Photo-Imageable) Mask                 |

| White Silk Screen (1 or 2 sides)                        |

| Maximum Size of 30 Square Inches                        |

| No Slots (or overlapping drill hits)                    |

| No Internal Routing (cutouts)                           |

| No Scoring, Tab Rout, or Drilled Hole Board Separations |

one of the internal layers. The three voltages are also used pretty commonly across the board, with 3.3V used the most, 2.5V the second most frequently, and 1.2 the least. Therefore, 3.3V will be the other power plane. The internal layers will be arranged as shown below in Figure 2.7.

Figure 2.7: 0.062" 4-Layer PCB Stack-Up

#### 2.3 Layout

When it comes time to start the layout of a PCB, it is important to take careful steps to insure that major changes do not have to be made at a later time. Simply thinking ahead about how different design decisions will affect future tasks, and planning ahead can save extraordinary amounts of time. For instance, if you know you are going to need 30 traces going through an area vertically, but only one horizontally, the 30 traces should get priority as to retain the original layer of routing. This is demonstrated in Figure 2.8 below. One can clearly see here that

Figure 2.8: Simple Design Routing Option Comparison

the bottom routing option is better. However, if the horizontal line were routed first, the design choice on the bottom may not have been made. This is why it is important to have foresight about the way in which future traces may be arranged. In fact, the same is true for component placement. If the peripheral does not require human interaction (such as a port, button, LED, or other interface), it is generally best to place the component in a place as close to the controlling device as possible without interfering with the path of other peripherals.

#### Chapter 3

#### DESIGN PROCESS - CADENCE ALLEGRO 16.2

This section of this thesis will discuss and describe in detail the recommended design flow when using the Cadence Allegro Design Tools Version 16.2. The tutorial will cover the general process for each step from pad development to PCB fabrication.

#### 3.1 Tutorial

In beginning to work with the Cadence Allegro Design Tools, the first step is to launch the project manager. Upon launch, a dialogue box will appear similar to the one shown below in Figure 3.1. Depending on the licenses that are available, there may more more or less selections. Unfortunately, the Allegro Suite was design

Figure 3.1: Cadence Allegro Product Choice Dialogue

for widespread use on a single project. Therefore, there are different product licenses for different functions. For instance, the Allegro PCB Librarian XL license provides

the most functionality for things like pad or part creation, while Allegro PCB Design HDL XL provides the most functionality for schematic editing and board layout. Allegro PCB SI XL is used mostly for signal integrity testing for high-speed devices. For creating a new project and getting started, choose PCB Librarian XL.

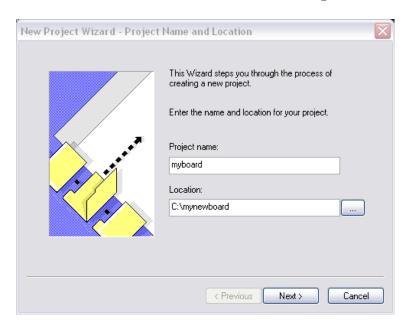

Now, the main project manager window is displayed. Here, select Create Design Project. Name the project something meaningful, and make sure that you pick a new unique folder on your hard drive that does not have any spaces in the file path. The window should now look similar to the one in Figure 3.2. Click next, and

Figure 3.2: Cadence Allegro New Project Location Dialogue

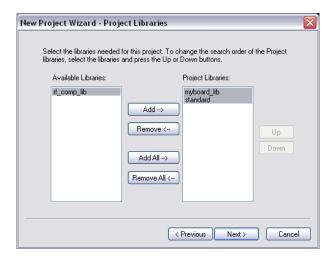

move the standard library to the available libraries. The standard library contains useful items such as a schematic page layout, ground and voltage terminals, etc. In large company projects, there are often many libraries with pre-created parts. However, if it is not known who created the design/part or if it was tested, it is generally not a good idea to use it in a design. Note that there is a library automatically created based on the project name. This library will hold all of the parts unique to the new design, and in this case all of the parts used. The window

should now look similar to the one in Figure 3.3. Click next again, and now Project

Figure 3.3: Cadence Allegro Project Library Dialogue

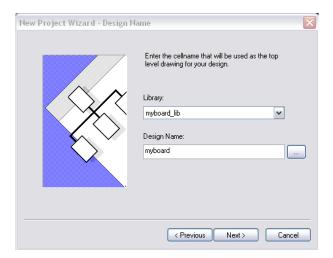

Manager will ask the user identify a cellname that will be the top level drawing in the design. Note that the new design library, in this case *myboard\_lib*, has already been selected. Now choose a name for the top level drawing in the design. The window should now look similar to the one in Figure 3.4. Now, click next and a

Figure 3.4: Cadence Allegro Top Level Drawing Dialogue

summary of the newly created project is presented. Look over the information and

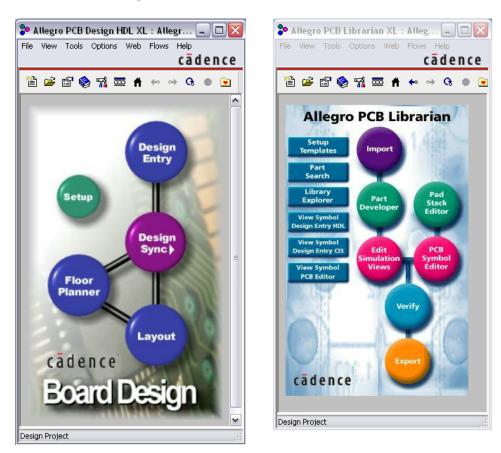

select finish when everything looks alright. Once the project has been created, a workflow will be presented similar to the one on the right shown below in Figure 3.5. The flow on the right is the flow when the PCB Librarian XL license is being

Figure 3.5: Cadence Allegro Project Manager Flow Window

used, while the flow on the left is when the PCB Design HDL XL license is being used. To switch between flows, simply click the Flows menu and select the flow you wish to see. Before getting started with part, symbol, and pad development, a few project settings need to be set. Cadence uses paths to specify where it will populate its list of available pads, symbols, and parts from. Enter the project settings by clicking Tools and then Setup. In the box that appears, click on the Tools tab. This should look similar to Figure 3.6. From here, open the PCB Editor Setup.

Figure 3.6: Cadence Allegro Setup Window Tools Tab

You will see here a list of categories on the left with many different things that are customizable about the software package. As mentioned before, it is necessary to modify the paths that Cadence uses to find its pads, symbols, and parts. Therefore, select the Paths category, and then the Library subcategory. In order to change where cadence looks for these files, we need to change the *psmpath* and the *padpath*. To change these default paths, click on the "..." button to the right of the title, and you will see a box similar to the one in Figure 3.7 below. Now create a folder inside the project folder and call it something like *syms&pads* to indicate that it will contain both pads and symbols. Now click the symbol to the left of the red X to create a new path, and enter the path of the previously created folder. Then click the new path and drag it to the top of the list, so that it is the first item in the directory list. This will make it the first place that Cadence checks for a referenced pad or symbol, and the one that takes precedence when there are duplicates. The same process will have to be followed for both the *psmpath* and the *padpath*. Once this is completed, simply click OK on both of the settings windows to return to the

project manager flow.

Figure 3.7: Cadence Allegro User Preferences Editor

#### 3.1.1 Step 1 - Pad Development

The next step in the design process is to create files that describe the physical holes or pads that the components in the design will be soldered to. This process begins with the component's data sheet. This section will describe the pad file creation process for several types of solder points in an attempt to cover any type of surface mount pad or through hole that one might come across. The first example component will be the PJ102AH power connector socket. The data

sheet is as shown below for this component in Figure 3.8. The measurement key is millimeters [inches]. Some data sheets have more or less information. This particu-

Figure 3.8: PJ102-AH Power Connector Socket Datasheet

lar data sheet contains precise measurements regarding pin placement and distance to the edge of the component. However, it is less than descriptive regarding the size of the holes. As one can see, the data sheet tells us that there are supposed to be three places where there is a 1mm X 1.6mm square hole. Unfortunately, there are not many foundries nor PCB design tools which provide for square holes, so it is best to avoid them if possible. To remedy this situation, simply use a circular hole, and make the size the largest dimension of any side of the proposed square hole. In this case, it is 1.6mm.

We begin by launching the Pad Stack Editor from the PCB Librarian flow. A prompt will appear asking for a name for the pad that will be created. Make sure that the name reflects information about the hole or pad, and information about what the pad/hole will be used for. First, set the units for this pad to millimeters to prevent having to convert from millimeters to mils. Then, If it is not already, set the hole type to 'Circle Drill', and the plating to 'Plated'. Then set the drill diameter to 1.6 millimeters. In the parameter box below, set the figure to 'Circle' and the width and height to 5 mils, or 0.127 millimeters larger than the drill diameter, totaling 1.727. Once this is completed, the window will look similar to the one in Figure 3.9.

Figure 3.9: Pad Stack Editor (Parameters Tab) for PJ102-AH Pad

Next, click on the 'Layers' tab. This is where the hole's parameters will be specified for each individual layer in the PCB board. First, click on the 'Begin Layer'. Now, in the bottom half of the window, change the geometry for each type of pad from 'Null' to 'Circle'. The regular pad should be 20 mils, or 0.508 millimeters, larger than the drill hole. So the regular pad width and height are changed to 2.108 millimeters. The 'Thermal Pad' and 'Anti-Pad' should be 20 mils larger than the regular pad, a total of 40 mils, or 1.16 millimeters larger than the drill hole. So now the width and height of the 'Thermal Pad' and 'Anti-Pad' are set to 2.760 millimeters.

Now that we have specified the parameters for the 'Begin Layer', we can copy those parameters to other layers which should have the same parameters. In this case, the internal and end layers should have the same parameters. To copy and paste these parameters, simply right-click on the column to the left of the layer name, and select 'Copy'. Then, do the same on the row you wish to move the information to, and select 'Paste'. The last two layers that need to be defined are 'SOLDERMASK\_TOP' and 'SOLDERMASK\_BOTTOM'. These layers need to be about 25 mils, or 0.635 millimeters, larger than the drill hole, and only the 'Regular Pad' should have parameters defined for it. Now, change the Geometry for SOLDERMASK\_TOP to 'Circle', and set the width and height to 2.235. Now, copy and paste this configuration to SOLDERMASK\_BOTTOM in the same manner as the previous settings. The window should now look similar to the one in Figure 3.10.

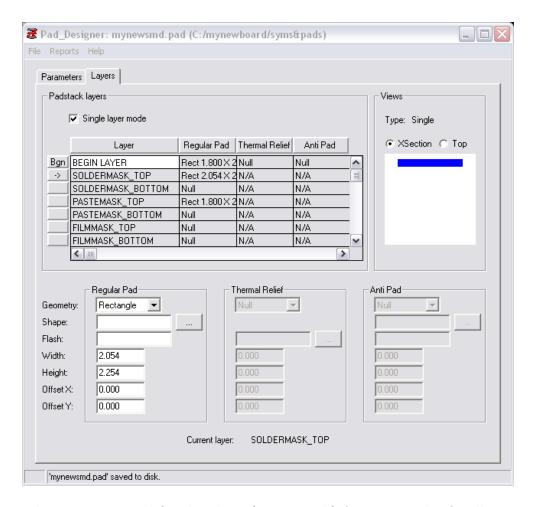

A similar procedure will be used to create the pads for another component, the Fox 50mhz Oscillator. Unlike the power connector socket, the oscillator is a surface mount part, meaning that it has no through/drill holes. Instead, the part is soldered one of the surfaces of the board. This allows for easier routing, although is generally slightly more difficult to solder. First, it is necessary to take a look at the data sheet, as many surface mount parts will sometimes have multiple different

Figure 3.10: Pad Stack Editor (Layers Tab) for PJ102-AH Pad

sized pads. The data sheet for this part is shown in Figure 3.11. Fortunately, all of the pads in the recommended solder pad layout have the same size, 1.8 mm X 2.0 mm. The process begins in a similar manner as before, by starting Pad Stack Editor from the PCB Librarian flow. This time, however, only the units need be changed on the 'Parameters' tab in the Pad Stack Editor. Simply change the 'Units' from 'Mils' to 'Millimeter'. Now click on the the 'Layers' tab. Since we will only be dealing with a surface layer, click the check box to turn on 'Single layer mode'. This will change the layer options to those suitable for describing a surface mount pad. First, click on the 'Begin Layer', and change the 'Regular Pad' geometry from 'Null'

# Recommended Solder Pad Layout 5.08 2.0 4.2

Figure 3.11: Fox 50mhz Oscillator Data Sheet

to 'Rectangle'. Then enter the recommended solder pad layout dimensions above into the width and height boxes. This defines the actual pad that will be soldered to.

Now, the 'PASTEMASK\_TOP' field should have the same parameters as the 'Begin Layer'. Therefore, use the same method as above to copy and paste the parameters. The paste mask is a layer which can be used to create solder paste screens for use in hot re-flow soldering systems. The last layer that needs to be defined for the surface mount pad is the 'SOLDERMASK\_TOP' layer. The solder mask layer is the protective coating found over everything except vias and pads. Defining a shape in this layer means there will be no protective coating placed over this region. For this reason, it is necessary to make this area slightly bigger than the pad itself. Generally this area is 10 mils, or 0.254 millimeters, larger than the pad. So, in the 'SOLDERMASK\_TOP' layer, set the geometry to 'Rectangle' and the dimensions to 2.054 mm X 2.254 mm. When this is completed, save the pad file. The window should look similar to the one in Figure 3.12. There are many other types of pads and through holes that can be created, but what is described here are the most common types.

Figure 3.12: Pad Stack Editor (Layers Tab) for Fox 50mhz Oscillator

## 3.1.2 Step 2 - PCB Symbol Development

The next step in the PCB creation process is to take the pads we just created and arrange them in the patterns described in the data sheets. The first step to accomplishing this is to plot out the location of the centers of each pin/pad in relation to the either the origin or the bottom leftmost corner of the footprint. Note that if the part only has 2 pins/pads or is a connector with a uniform pin/pad layout, a wizard can be used with only a few standard dimension measurements to produce the desired pin/pad layout. Cadence uses a standard cartesian coordinate system for object placement, so plotting out all of the coordinates ahead of time is

quite useful. As an example, the PJ102-AH Power Socket will be used.

Now, start the PCB Symbol Editor from the PCB Librarian flow. Click File - New from the menu. This will bring up a new file menu. Select 'Package Symbol' as the drawing type, and type in a name for the new symbol. Click the OK button, and a blank new package symbol appears. Before beginning pin/pad placement, it is helpful to change a few settings. First, click Setup - Design Parameters. In the first tab, the 'Display' tab, there are several options that can be very beneficial when turned on. The grids, for example, are especially helpful when placing components by hand. To use grids, first check the 'Grids On' box, and then click the '...' button next to the Setup Grids label. This window allows you to change the distance between the gridlines, which the cursor will snap to when placing objects by hand. It is very useful to change the grids during the design process. Note that right now, the measurements are set to mils. Click OK to return to the 'Design Parameters' window. Now go to the 'Display' tab. Here, the units used in the design can be changed. Since the measurements in the data sheet are in millimeters, it will be most convenient to use millimeters in the symbol development process as well. In this tab, the extents of the working canvas can be changed, as well as the origin of the project. Note that values entered in the 'Move Origin' box denote the change in the X or Y direction, and not the new origin point. This window contains other tabs which allow for the adjustment of many default values that can help make the experience feel more streamlined. Adjust the settings as necessary, and click OK to return to the main window.

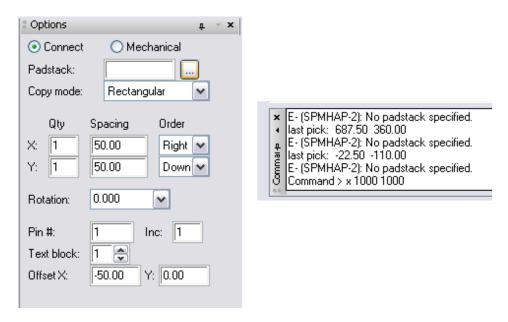

The next step to creating a PCB symbol is to place the pins. This is where the coordinates come in very handy. It is also important to place the pins in the order that they are numbered; for example, place pin one first, pin two second, etcetera. This will save time in having to go back and change the pin numbers later. To instantiate a pin, click *Layout - Pins*, and a sidebar menu should appear on the

righthand side of the window that contains options for pin placement. Click the '...' button to the left of the 'Padstack' field and select the pad you want to place. Below this, there are many useful options for placing a large number of pins spaced equidistantly from one another, rotating a pad, numbering those pads, and offsetting them from each other. This set of tools proves invaluable in instances where a large number of pins or pads are to be placed. However, there is no need to change any of these settings in this case. Now it is time to place pin 1. This can be done simply using the mouse, but this is highly inaccurate unless measurements are in all whole numbers, something that rarely occurs. It is best to enter the coordinates manually. Simply click at the bottom of the tool in the command window and type 'x x-coord y-coord'. For example, if I wished to place the first pin at 'X=1000 Y=1000', i would type 'x 1000 1000', as shown in Figure 3.13. Simply repeat this process until

Figure 3.13: Allegro PCB Editor (Package Symbol) Pin Placement Procedure

all pins/pads are placed where they are supposed to be. When pin placement is complete, right-click an unpopulated area on the canvas and select 'Done'. When

the tool is an a "mode" such as 'Pin Placement Mode', it will stay in that mode until 'Done' is selected.

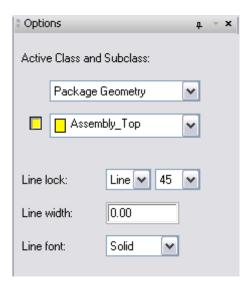

At this point, the pins are in place, and this symbol could technically be used on a PCB. However, there is no indication at this point in time of where the physical part will extend to and cover. Without some kind of guideline, a designer could easily place other components, such as surface mount resistors, in an area which will interfere with the component. To prevent this, a package geometry line will now be created. To do this, click Add - Line. This will bring up a specific options menu on the righthand side of the window. In this menu, select 'Package Geometry' as the active class, and 'Assembly\_Top' as the subclass. The line width and font should already be set to 0 and solid, respectively. The line lock is useful for drawing lines with the mouse. This feature allows the possible angles to be locked such that lines and arcs can only be drawn using the specified angle. This is not necessary in this case, as the component is square, and we will be specifying the vertices using the coordinate specifier. The options window should look similar to Figure 3.14. Now, enter the coordinates one by one, ending on the starting

Figure 3.14: Allegro PCB Editor (Package Symbol) Line Options

coordinates. Right-click on an unpopulated area of the canvas and select 'Done' when finished.

Some designers also like to create a silkscreen outline of the part, however some do not. This next step, therefore, is not necessary. If a silkscreen outline is desired, begin bringing up the line options menu by following the same procedure as for the package geometry line. This time, however, select 'Silkscreen\_Top' as the subclass, keeping 'Package Geometry' as the active class. Now, enter the coordinates or use the mouse to draw another box around the component. The box can be the exact dimensions and coordinates as the package geometry line. Now that there a visual indicator of the package size, as well as an optional silkscreen indicator, it is also necessary to provide Allegro with a package boundary. A package boundary defines the area in which no other components may be placed. This is useful in parts such as the PJ102-AH power connector, because some of the pins extend out past the actual package geometry, and it is preferable to keep neighboring components a safe distance away. To define this boundary, click Setup - Areas - Package Boundary. As before, a special options window appears. In this case, however, it is not necessary to set the options, as they are already correctly configured. Simply draw a boundary box using the mouse, or by entering coordinates.

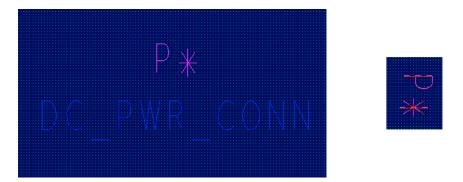

The next step is to place labels around and inside the symbol. The first label to place is the reference designator. This label will go inside of the package geometry, and it is for the reference of the designer only; it will not appear on the fabricated board. Place this label by clicking Layout - Labels - RefDes. As before, an panel will appear on the right side of the window containing various text options. It can be useful to change some of these options before clicking the point at which to place the text, such as center justification. When options have been set, click where the start point of the text should go. If the text is not placed correctly the first time, it can be changed later. This label should designate the type of component or device,

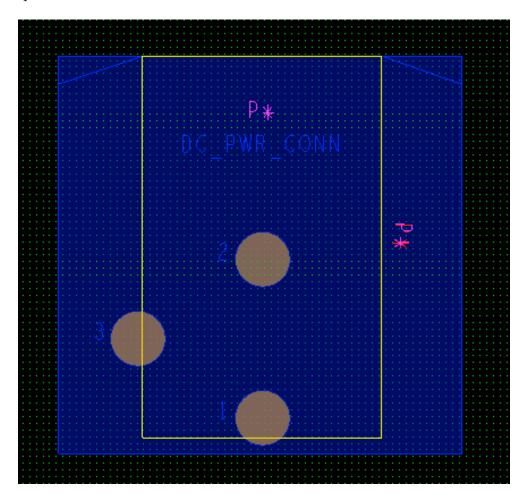

as well as the instance number. Because this is a power connector, 'P' will be used to precede the instance number. In Allegro, the wildcard '\*' is used to denote instance number, and will be replaced by the tool later. Therefore, type 'P\*' as the text for this label. When finished it should look similar to the one shown in Figure 3.15. Another label that is helpful to the designer is the device type label. To set this label, click Layout - Labels - Device, and follow the same procedure as above to place the label inside the package geometry. This label should contain something about the package type, if it is a standard package type, such as the 0805 or SSOP16. In this case, the type is unique to the device, so something such as 'DC\_PWR\_CONN' will do nicely. The last label will be visible on the end product, and is also a reference designator. This label will prove very useful when placing components, as often there are many different parts that need to be soldered to the same footprint type. To place this final label, click Layout - Labels - RefDes. In the options panel that appears on the right side of the window, select 'SILKSCREEN\_TOP' as the subclass. Now place a label outside of the device, and give it the same designation as the first reference designator, 'P\*'. Rotate the text as necessary and when finished, exit label placement mode as previously described. The completed labels should look similar to those below in Figure 3.15.

Figure 3.15: Allegro PCB Editor (Package Symbol) PJ102-AH Completed Labels

The completed symbol should look similar to that of Figure 3.16. Note that

the colors can be changed to the designer's liking by clicking *Display - Colors/Visibility*. Simply save the design (ensure that it is in the project's work library OR your symbols and pads folder so that Allegro will search there) and continue on to part development.

Figure 3.16: Allegro PCB Editor (Package Symbol) PJ102-AH Completed Symbol

# 3.1.3 Step 3 - Part Development

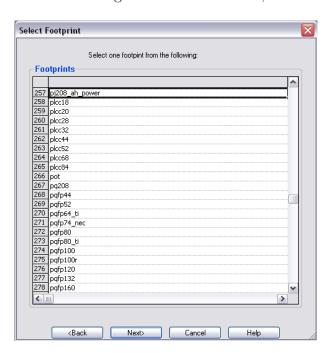

Now that the symbol for the part has been created, the next step is to create a complete part. When completed this part entity will contain all of the pin names that describe what each pin on the device is used for, as well as a symbol that can be instantiated in schematic editor in order to describe the connections to other components that will be routed in the final design. Begin by starting Part Developer from the PCB Librarian XL flow. This will bring up the utility with an empty screen. To begin creating a part, select File - Import and Export. A dialogue will pop up, asking you to select an action to perform. Select 'Import Cadence Footprint'. In the flow, as well as in the previous flow, the 'Footprint' to which Allegro is referring was called a 'Package Symbol'. They are the same thing, and most often in other programs and documentation, it is referred to as a 'Footprint'. For the purposes of this tutorial, the PJ102-AH footprint created in the previous step, as well as the footprint for the Fox 50mhz oscillator, are used as a demonstration. Once the footpring has been selected, click the next button, noting that Allegro is capable of importing from a great number of sources to create a part file that can be used in the tools. Select the symbol, or footprint, that was created in the previous step. An example of this is shown in Figure 3.17. Click Next, and enter the name of the

Figure 3.17: Allegro Part Developer - Importer Footprint Selection

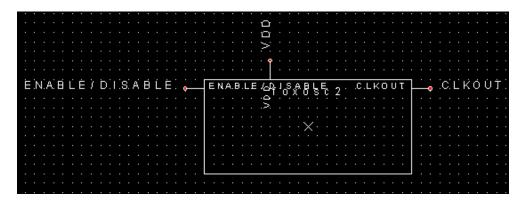

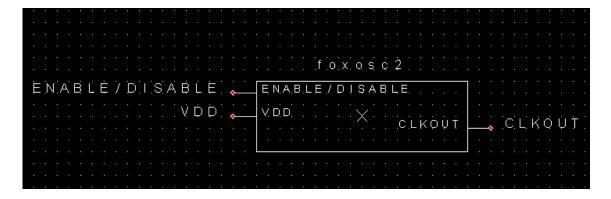

part, or use the same name as the footprint. The project library should be set by default as the destination library. Click next again, and there is a preview of the pins that will be imported. It is recommended, but not required, that the type of each pin as well as the name be entered at this time. There is also the opportunity now to specify global pins. Global pins are those which do not need to be specified explicitly in the schematic phase, but are recognized as nets and will be eventually routed as such. The common use for global pins is for pins which will be connected to power planes or power nets, as well as ground nets. This can be done in this step of the import wizard. Simply right click inside the global pins box, and choose 'Insert Row After' one time for each signal that needs to be global. Specify the net name, type, and the pins which are to be connected to that net. The original entries for those pins must be deleted from the 'Logical Pins' section so that the pins are not mapped twice. Because the PJ102-AH is a power socket, all of its pins are global. This window for the Fox 50mhz oscillator is also shown below in Figure 3.18 for reference. Once this is completed, the window for either of these two parts should

Figure 3.18: Allegro Part Developer - Importer Pin Assignment

look similar to Figure 3.18. Not that the window for the Fox 50mhz oscillator has 'VDD' in the 'Logical Pins' area. This is because while the pin will be connected to the 'VCC3V3' net, it has a bypass capacitor connected to it. If in the schematic stage the bypass capacitor is connected directly to this net on the symbol, Allegro will make this connection explicit, and will display a rat to help during component placement. Now, click the 'Finish' button to commit these settings.

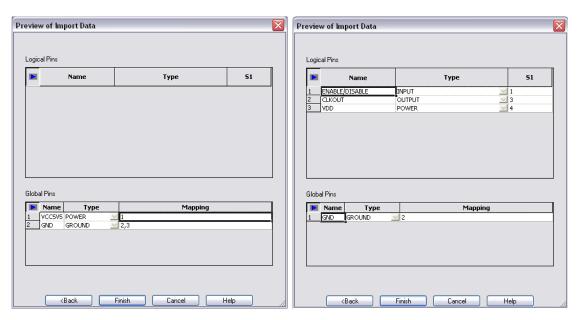

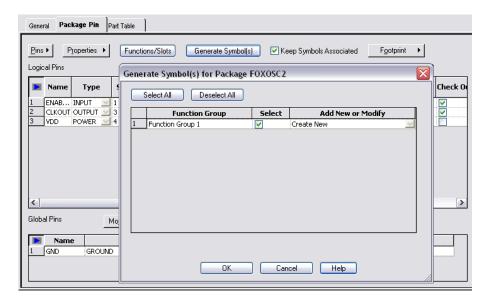

The screen for the new part should appear. The part developer tool provides many opportunities to enter design-specific constraints that can aid invaluably in the prevention of errors throughout the design process. It is now necessary to generate schematic symbols for the part we have just created. In larger designs,

Figure 3.19: Allegro Part Developer - Generate Symbol(s) Dialogue

where there are hundreds of pins, it is desirable to split the pins across multiple schematic symbols. This can be accomplished by clicking the 'Functions/Slots' button. A new window will appear that has a list of the function groups that exist currently. To add function groups, simply click the add button as many times as is necessary. When the desired amount of function groups appears in the window, click the 'Distribute Pins' button. This will bring up yet another window that

allows the distribution of the pins for a particular part across the function groups that were just specified. To move several pins at once to a particular function group, highlight the rows, and then right click and hit 'Move to...'. Once the pins have been distributed, click OK to return to the original window. In this case distributing the pins is not necessary, as both of the parts have less than five pins. To generate a symbol, click the 'Generate Symbol(s)' button. This should produce a dialogue as shown in Figure 3.19. This produces a basic schematic symbol from the data provided during the import wizard. To view the symbol generated, click 'sym\_1' in the hierarchy on the left. The symbol should look something like the one shown in Figure 3.20, very disorganized, confusing an rudimentary. Depending on the configuration, a generated symbol may look acceptable. However in many cases, such as this one, the generated symbol needs modification before it is used. Using the provided interface, modify the symbol so that all of the pin labels are

Figure 3.20: Allegro Part Developer - Initial Generated Symbol

readable, and the symbol description is not obstructing the pin labels. This can be accomplished by changing the pin positions, label positions, text size, pin locations, and the symbol outline. When this has been completed, the symbol should look clean, and the pins easy to identify and logically ordered. An example of a cleaned up rendition of the symbol shown above is in Figure 3.21.

Figure 3.21: Allegro Part Developer - Modified Generated Symbol

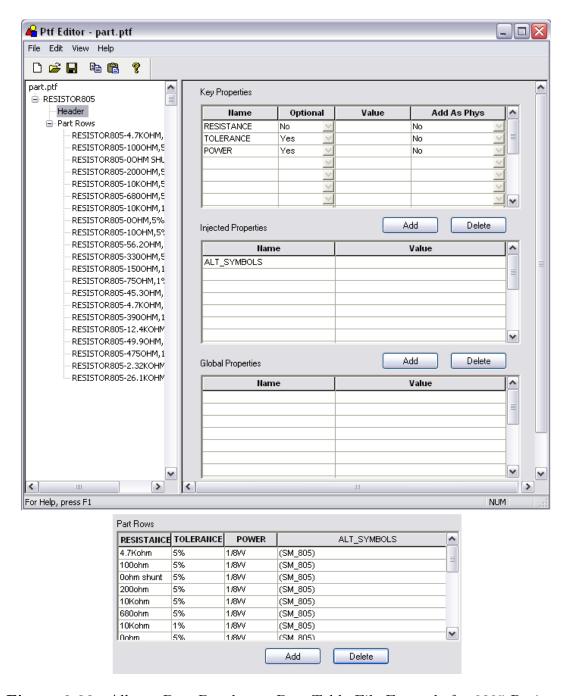

For this particular part, the part creation process is finished. Simply click File - Save to write the file to the project's working folder. However for parts such as a resistor or capacitor, where there are many values for the same part, it is necessary to create a part table. To do this, right click on 'Part Table Files' and select 'New'. This will create a new part table, and launch the PTF Editor. Once the PTF Editor has fully loaded, click the '+' symbol next to the name of the part, in this case 'RESISTOR805', then click on Header and fill in the data as shown below in Figure 3.22. Of course, these values can be modified to meet the requirements of a particular part, such as a capacitor or LED. Fields can be added for other parameters if desired by the designer. This can be very useful when dealing with parts that have very subtle differences. Next, click on the Part Rows on the left. Now click add for each different set of values until all of the required parts have been entered. This should look similar to the one below in Figure 3.22. Now click File - Save or File - Exit and select 'Yes' when asked if the file should be saved or not. Part Developer will then reload the part file, and when save, the part now contains a part table. It is now appropriate to continue to schematic development.

Figure 3.22: Allegro Part Developer -Part Table File Example for 0805 Resistor

### 3.1.4 Step 4 - Schematic Development

Once all of the parts necessary for the design have been saved into the design library, it is time to begin entering design schematics. In the 'Project Manager', it is necessary to change the product license by clicking File - Change Product.... The 'Allegro PCB Design HDL XL' provides the optimal set of options for entering schematics. Select this license and hit OK. The click Flows - Board Design, which will bring up the board design flow. Now startup the schematic editing tool Design Entry HDL by clicking the 'Design Entry' button. When Design Entry HDL has finished loading, there are a few things to make the experience more user-friendly. Right click in the workspace, and select 'Add Component'. In the component browser that appears, click Configuration - Setup. In the left pane, click 'Details' and check the box next to 'Minimize on Add', and click OK. Now click View - Single Detail Tab. In the 'Browse Libraries' screen, select the 'standard' library. This library contains special symbols commonly used for creating schematics, including 'VCC' and 'GND'. In order to keep the schematics organized and contained, a symbol in the standard library will be used. Click the cell 'b size page' and then click 'Add'. use the cursor to place this frame anywhere on the page. This object is exactly the size of an 11x17 sheet of paper. Therefore, designs can be easily printed when the time comes with nicely formatted labels that state the nature of the work, and its designer(s). To place these labels, first use the zoom tools (the 'Zoom Points' tool is especially useful in the case) to center around the label section in the bottom righthand corner of the object. Then bring up the text placement window by clicking Text - Note.... This should produce a window similar to the one shown below in Figure 3.23. In the text placement window, type the page title, designer name, date, and page number into the text box, separated by carriage returns as shown in the figure. Now use the mouse to place the labels inside the boxes they belong in. Allegro seems to lock these labels into a default

Figure 3.23: Allegro Design Entry HDL - Note Entry Window

position, and when finished, the labels will look similar to those below in Figure 3.24. When the labels are in place, it is time to begin entering schematics. To

Figure 3.24: Allegro Design Entry HDL - Page Labels

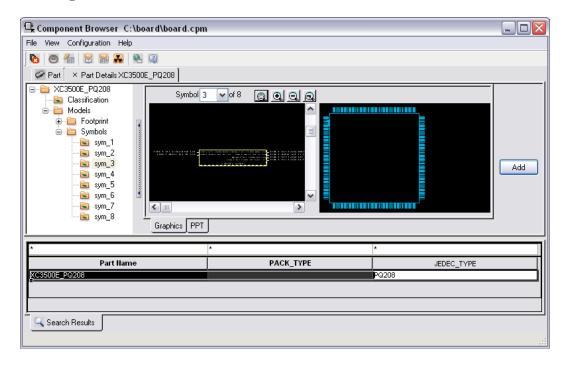

add components to the page, follow the same procedure as used before to add the page layout. This time, however, select the library associated with the project (for example *myboard\_lib*) and choose the component you wish to add. Then place it in the schematic in a logical location. When dealing with components that have multiple symbols, or components that have multiple part values, click on the part in the table in the bottom half of the screen. This will bring up the part details tab for this part. In this tab, the different symbols available can be viewed via the dropdown menu, and when the correct symbol has been found it can be added to

the workspace in the same fashion as the page layout. The part details tab can be seen in Figure 3.25 below.

Figure 3.25: Allegro Design Entry HDL - Component Browser Part Details Tab

Draw connections between components by selecting the 'Draw Wire' tool from the toolbar, and then clicking to form right angled paths between two points. To connect to a pin on a component, click directly on the terminal of that pin. To tap off of another wire, simple click on the wire at the point you wish to tap from. This types of connections will look similar to the ones below in Figure 3.26. For bus wires (denoted by thicker lines), Allegro makes it easy to connect a bus to another bus of the same size. However, if the source or destination does not have a bus input, then it may be necessary to tap the bus to bring out the individual components. This is very simple to do with Design Entry HDL. Simply bring the bus along the area in which you wish to break out the bus. Usually, when a bus is tapped, the wires are tapped in numerical order. The tool makes it very easy to tap in this fashion. To add a bus tap, simply click Wire - Bus Tap..., and then click on

**Figure 3.26:** Allegro Design Entry HDL - Example of Simple Schematic Connections

the point on the bus closest to the destination pin/point, and then the destination pin/port. Do this until the correct number of taps have been created. Note that at this point, there are only '?' next to the taps. This is because the particular wire within the bus that is being tapped has not been assigned yet. To assign the wires, click Wire - Bus Tap Values... Select the most significant bit, and the least significant bit (start and end points), and the increment between consecutive taps. Then, click outside of the starting bus tap on the side away from the other bus taps to be labeled. Now, click outside of the last bus tap on the side away from the other bus taps. All of the taps will now be automatically labeled. An example of a completed tapped bus is shown below in Figure 3.27. To name any net in the design, simply click Wire - Signal Name. The procedure for placing the signal names is similar to that of labels. After typing in the signal name, click on the wire to be named.

To create additional schematic pages, click on the last page in the 'Hierarchy Viewer' on the left of the Design Entry HDL window. Then click in the menu bar File - Edit Page/Symbol - Add New Page. Then make sure to save the page, so it shows up in the 'Hierarchy Viewer'. Follow the same procedure as before

Figure 3.27: Allegro Design Entry HDL - Example of Bus Tapping

to instantiate a page layout and draw schematics for the design. When design schematics are complete, ensure that all schematic pages are saved, and then close the Design Entry HDL, and move on to the PCB Layout Stage.

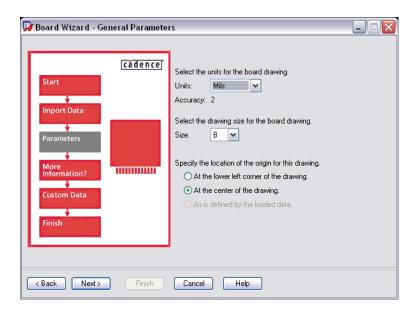

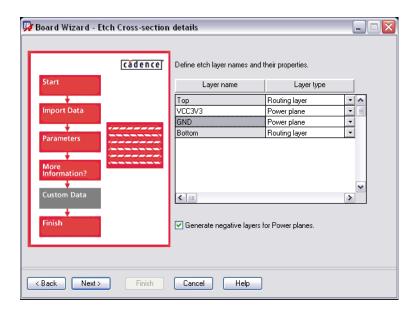

# 3.1.5 Step 5 - PCB Layout