# DARTS: A RUNTIME BASED ON THE CODELET EXECUTION MODEL

by

Joshua Suetterlein

A thesis submitted to the Faculty of the University of Delaware in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering

Spring 2014

© 2014 Joshua Suetterlein All Rights Reserved UMI Number: 1565392

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI 1565392

Published by ProQuest LLC (2014). Copyright in the Dissertation held by the Author.

Microform Edition © ProQuest LLC. All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 - 1346

## DARTS: A RUNTIME BASED ON THE CODELET EXECUTION MODEL

by

Joshua Suetterlein

Approved:

Guang R. Gao, Ph.D. Professor in charge of thesis on behalf of the Advisory Committee

Approved:

Kenneth E. Barner, Ph.D. Chair of the Department of Electrical and Computer Engineering

Approved: \_

Babatunde A. Ogunnaike, Ph.D. Dean of the College of Engineering

Approved: \_

James G. Richards, Ph.D. Vice Provost for Graduate and Professional Education

### TABLE OF CONTENTS

| LI       | ST C  | OF FIC           | BLES                                                                                  |

|----------|-------|------------------|---------------------------------------------------------------------------------------|

| C        | hapte | er               |                                                                                       |

| 1        | INT   | RODU             | UCTION                                                                                |

| <b>2</b> | BA    | CKGR             | OUND                                                                                  |

|          | 2.1   | Datafl           | ow                                                                                    |

|          |       | 2.1.1            | Static Dataflow                                                                       |

|          |       |                  | 2.1.1.1Dataflow Graphs62.1.1.2Operational Semantics72.1.1.3Limits of Static Dataflow8 |

|          |       | $2.1.2 \\ 2.1.3$ | Dynamic Dataflow8Argument Fetching9                                                   |

|          | 2.2   | EART             | Ή 10                                                                                  |

|          |       | 2.2.1            | EARTH Threading Model                                                                 |

|          |       |                  | 2.2.1.1       Fibers       10         2.2.1.2       Threaded Procedures       11      |

|          |       | 2.2.2<br>2.2.3   | EARTH Architecture Model11EARTH's Advantages13                                        |

| 3        | CO    | DELE             | $\Gamma$ MODEL                                                                        |

|          | 3.1   | Codele           | et Abstract Machine Model                                                             |

|   | 3.2 | Threa | ding Model                                                                                   | 16 |

|---|-----|-------|----------------------------------------------------------------------------------------------|----|

|   |     | 3.2.1 |                                                                                              | 16 |

|   |     | 3.2.2 | 1                                                                                            | 17 |

|   |     | 3.2.3 | The Ideal Codelet                                                                            | 18 |

|   |     |       | 3.2.3.1 Non-Preemptive                                                                       | 18 |

|   |     |       | 3.2.3.2 Well-Behaved CDGs                                                                    | 19 |

|   |     |       | 3.2.3.3 Well-Formed CDGs                                                                     | 20 |

|   |     | 3.2.4 | Threaded Procedure                                                                           | 20 |

|   |     | 3.2.5 | Loop                                                                                         | 21 |

|   | 3.3 | Codel | et Architecture Model                                                                        | 21 |

|   |     | 0.0.1 |                                                                                              |    |

|   |     | 3.3.1 | 5                                                                                            | 23 |

|   |     | 3.3.2 | 1                                                                                            | 23 |

|   |     | 3.3.3 |                                                                                              | 24 |

|   |     | 3.3.4 | Memory and Interconnect                                                                      | 24 |

| 4 | DA  | RTS . |                                                                                              | 26 |

|   | 4.1 | Imple | mentation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $2$                          | 26 |

|   |     | 4.1.1 | Codelets                                                                                     | 26 |

|   |     | 4.1.2 | Threaded Procedures                                                                          | 27 |

|   |     | 4.1.3 | Loops                                                                                        | 29 |

|   |     |       | 4.1.3.1 Serial loop                                                                          | 30 |

|   |     |       | ±                                                                                            | 32 |

|   |     |       |                                                                                              | 35 |

|   | 4.2 | Runti | me                                                                                           | 37 |

|   |     | 4.2.1 | Schedulers                                                                                   | 37 |

|   |     |       | 4.2.1.1 TP Scheduler                                                                         | 37 |

|   |     |       |                                                                                              | 39 |

|   |     |       |                                                                                              | 40 |

|   |     |       |                                                                                              | 41 |

|   |     |       | 4.2.1.4.1 Static                                                                             | 41 |

|   |     |       |                                                                                              |    |

|   |     |       | $4.2.1.4.2  \text{Dynamic}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 42 |

|     |                                                                                   | 4.2.1.4.3                             | Work Stealing 43                                                                                                                                                                                                               |

|-----|-----------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | $4.2.2 \\ 4.2.3$                                                                  |                                       |                                                                                                                                                                                                                                |

| 4.3 | API                                                                               |                                       |                                                                                                                                                                                                                                |

|     | $\begin{array}{c} 4.3.1 \\ 4.3.2 \\ 4.3.3 \\ 4.3.4 \end{array}$                   | Affinity                              | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                          |

| 4.4 | Examp                                                                             | ole                                   |                                                                                                                                                                                                                                |

|     | $ \begin{array}{r} 4.4.1 \\ 4.4.2 \\ 4.4.3 \end{array} $                          | Fibonacci Codelets                    |                                                                                                                                                                                                                                |

| 4.5 | Micro                                                                             | Benchmarks                            |                                                                                                                                                                                                                                |

|     | $\begin{array}{c} 4.5.1 \\ 4.5.2 \\ 4.5.3 \\ 4.5.4 \\ 4.5.5 \\ 4.5.6 \end{array}$ | Monica                                | 58         50         50         50         50         51         51         52         53         54         55         56         57         58         58         58         59         50         51         52         52 |

|     | 4.5.7                                                                             | 4.5.6.2 Monica .<br>4.5.6.3 Codelet F | 60                                                                                                                                                                                                                             |

|     |                                                                                   | 4.5.7.1 Mills<br>4.5.7.2 Monica       | 68<br>                                                                                                                                                                                                                         |

|     | 4.5.8                                                                             | Codelet Chain                         |                                                                                                                                                                                                                                |

|     |                                                                                   | 4.5.8.1 Mills                         |                                                                                                                                                                                                                                |

|          |              |                  | 4.5.8.2                  | Monica            |      |      |     |    | •   | •   | <br>    | • | <br>• | <br>• | • | 75       |

|----------|--------------|------------------|--------------------------|-------------------|------|------|-----|----|-----|-----|---------|---|-------|-------|---|----------|

|          |              | 4.5.9            | TP Chai                  | n                 |      |      |     |    |     |     | <br>    | • |       |       |   | 76       |

|          |              |                  | 4.5.9.1<br>4.5.9.2       | Mills .<br>Monica |      |      |     |    |     |     |         |   |       |       |   | 77<br>78 |

|          |              | 4.5.10           | Tree                     |                   |      |      |     |    | •   |     | <br>    | • |       |       |   | 79       |

|          |              |                  | 4.5.10.1<br>4.5.10.2     |                   |      |      |     |    |     |     |         |   |       |       |   | 81<br>82 |

| <b>5</b> | CA           | SE ST            | UDIES .                  | ••••              |      |      |     |    |     | ••• | <br>    | • |       | <br>• |   | 84       |

|          | $5.1 \\ 5.2$ |                  | k Multiply<br>th First S |                   |      |      |     |    |     |     |         |   |       |       |   | 84<br>88 |

| 6        | RE           | LATEI            | ) WORF                   | ζ                 |      |      |     |    |     |     | <br>    | • |       |       |   | 92       |

|          | 6.1          | SWAR             | RM                       |                   |      |      |     |    |     |     | <br>    | • |       |       |   | 92       |

|          |              | $6.1.1 \\ 6.1.2$ | SWARM<br>Locality        |                   | -    |      |     |    |     |     |         |   |       |       |   | 92<br>93 |

|          | 6.2          | -                | Communi                  | v                 |      |      |     |    |     |     |         |   |       |       |   | 94       |

|          | 6.3          |                  | rrent Coll               |                   |      |      |     |    |     |     |         |   |       |       |   | 95       |

|          | 6.4          |                  | s and Ope                |                   |      |      |     |    |     |     |         |   |       |       |   | 95       |

|          | 6.5          |                  | ıla                      |                   |      |      |     |    |     |     |         |   |       |       |   | 96       |

|          | 6.6          |                  | Threading                |                   | -    |      |     |    |     |     |         |   |       |       |   | 97       |

|          | $6.7 \\ 6.8$ |                  | n++<br>                  |                   |      |      |     |    |     |     |         |   |       |       |   | 97<br>98 |

|          | 6.9          | 0                | reeze                    |                   |      |      |     |    |     |     |         |   |       |       |   | 98       |

| 7        | CO           | NCLU             | SION A                   | ND FU'            | TURE | E WO | )RF | ζ. |     |     | <br>    |   |       |       |   | 101      |

| B.       | IDLI         | υσκα             | PHY                      |                   |      |      |     |    | • • | • • | <br>• • | • |       | <br>• | • | 102      |

## LIST OF TABLES

| 4.1 | DARTS' TP Overhead                                        | 57 |

|-----|-----------------------------------------------------------|----|

| 4.2 | DARTS' Codelet Total Overhead                             | 58 |

| 4.3 | DARTS' Codelet Scheduling Overhead                        | 59 |

| 4.4 | Speedup of Non-Strict Tree over Strict Tree on Mills      | 82 |

| 4.5 | Speedup of Non-Strict Tree over Strict Tree on Monica     | 83 |

| 5.1 | DARTS speedup over ACML's OpenMP DGEMM                    | 86 |

| 5.2 | DARTS' Speedup Over OpenMP BFS Reference Implementation . | 91 |

### LIST OF FIGURES

| 2.1  | Dataflow Graph Example                                      | 7  |

|------|-------------------------------------------------------------|----|

| 2.2  | EARTH Architecture Model                                    | 12 |

| 3.1  | Codelet Abstract Machine Model                              | 15 |

| 3.2  | Codelet Graph Example                                       | 18 |

| 3.3  | Codelet Architecture Model                                  | 22 |

| 4.1  | Codelet For Loop Example                                    | 33 |

| 4.2  | Parallel For All Loop Example                               | 35 |

| 4.3  | DARTS Runtime Diagram                                       | 38 |

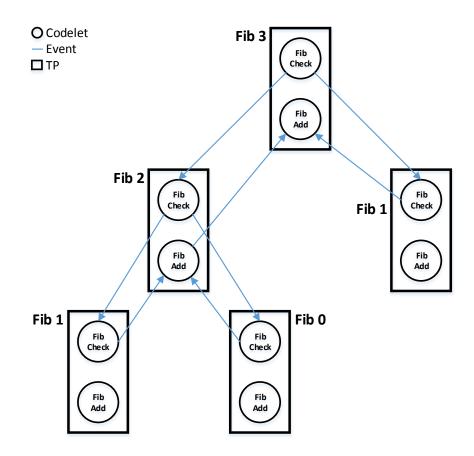

| 4.4  | Codelet Fibonacci Example                                   | 54 |

| 4.5  | DARTS' Initialization Overhead                              | 57 |

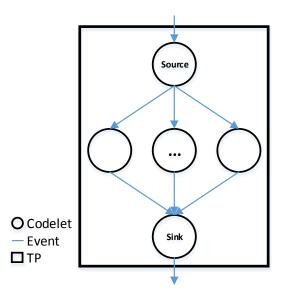

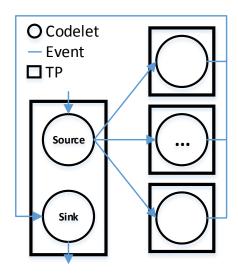

| 4.6  | Codelet Fanout Pattern                                      | 60 |

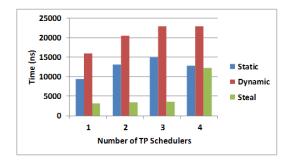

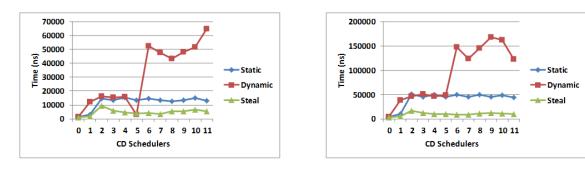

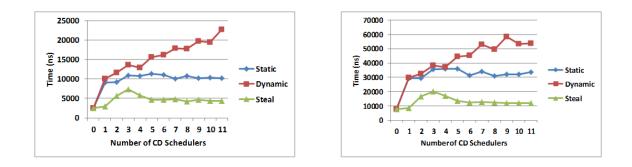

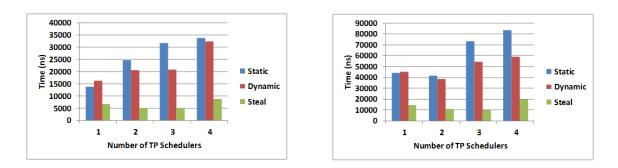

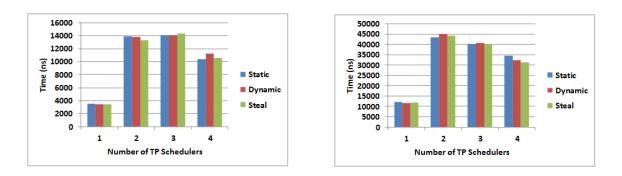

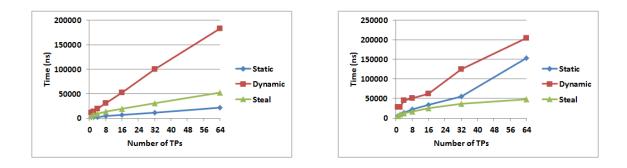

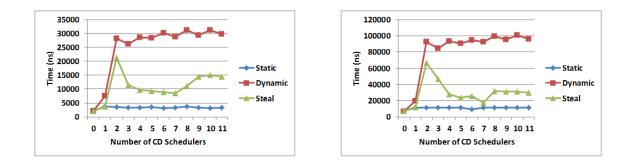

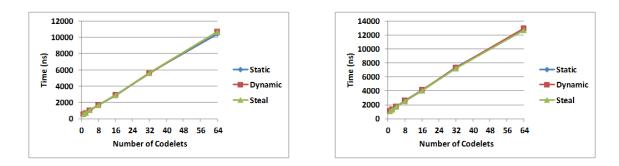

| 4.7  | Codelet Fanout Pattern on a Single Mills Cluster            | 61 |

| 4.8  | Codelet Fanout Pattern Using Multiple Mills Clusters        | 61 |

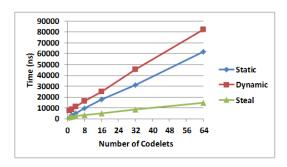

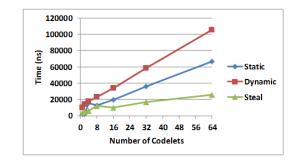

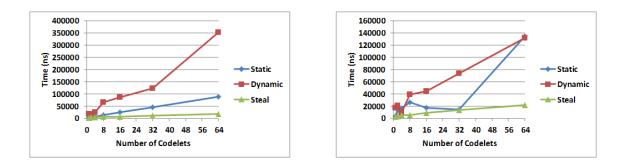

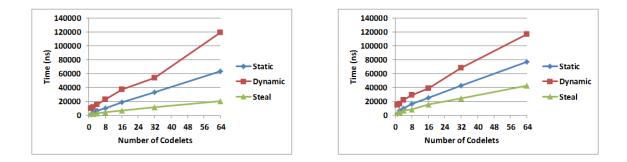

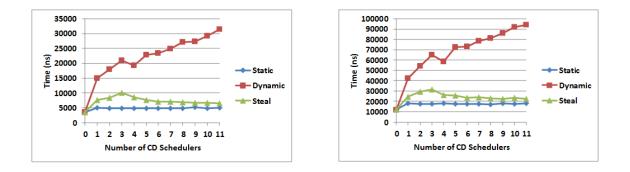

| 4.9  | Codelet Fanout Pattern on Mills Scaling Number of Codelets  | 62 |

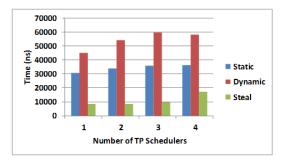

| 4.10 | Codelet Fanout Pattern on a Single Monica Cluster           | 63 |

| 4.12 | Codelet Fanout Pattern on Monica Scaling Number of Codelets | 63 |

| 4.11 | Codelet Fanout Pattern Using Multiple Monica Clusters       | 64 |

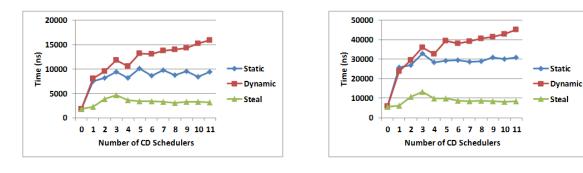

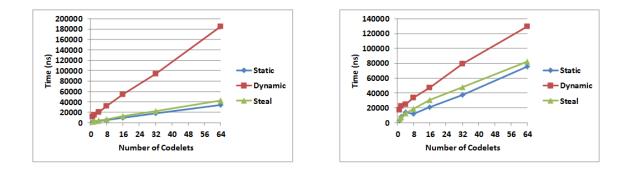

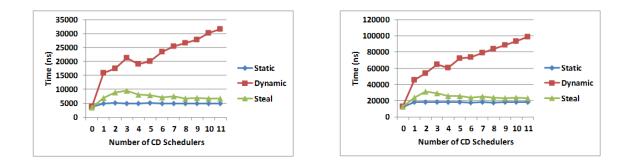

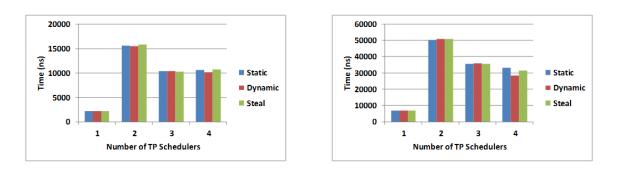

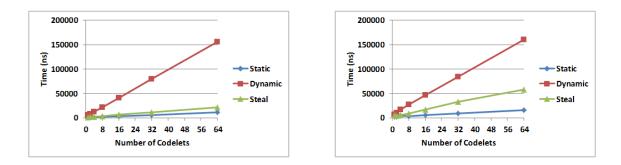

| 4.13 | Codelet For Loop Running on Mills                           | 65 |

| 4.14 | Codelet For Loop Running on Monica       | 66 |

|------|------------------------------------------|----|

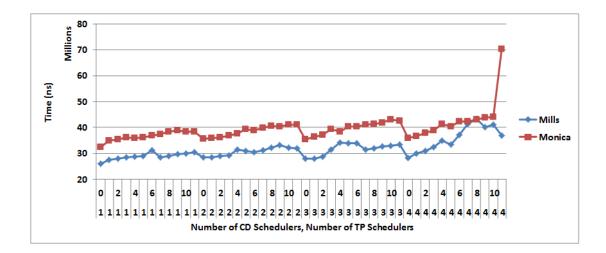

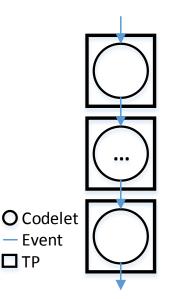

| 4.15 | TP Fanout Pattern                        | 67 |

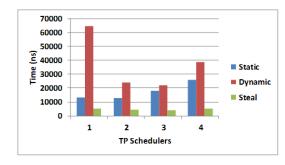

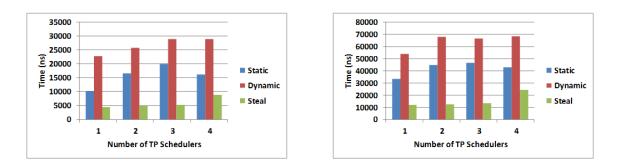

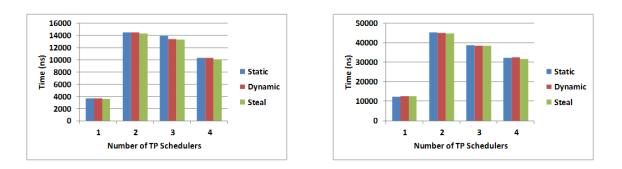

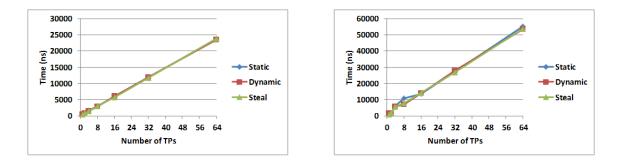

| 4.16 | TP Fanout Pattern Running on Mills       | 69 |

| 4.17 | TP Fanout Pattern Running on Monica      | 70 |

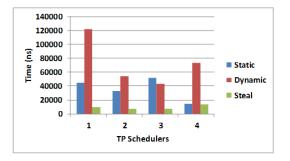

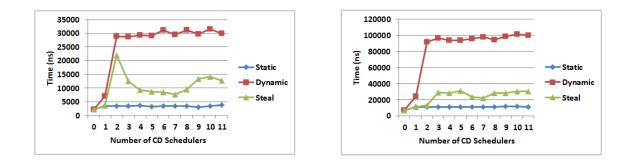

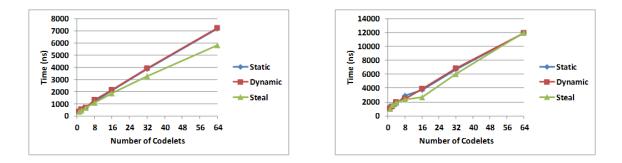

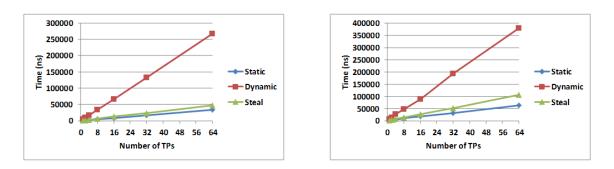

| 4.18 | TP For Loop Running on Mills             | 72 |

| 4.19 | TP For Loop Running on Monica            | 73 |

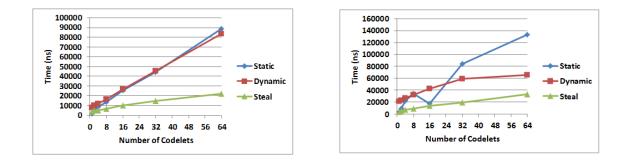

| 4.20 | Codelet Chain Pattern                    | 74 |

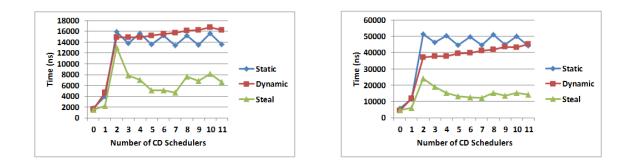

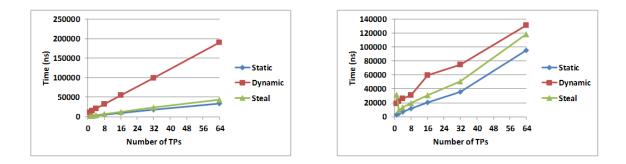

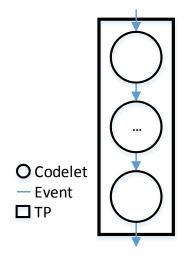

| 4.21 | Codelet Chain Pattern Running on Mills   | 75 |

| 4.22 | Codelet Chain Pattern Running on Monica  | 76 |

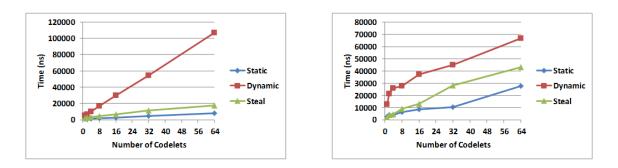

| 4.23 | TP Chain Pattern                         | 77 |

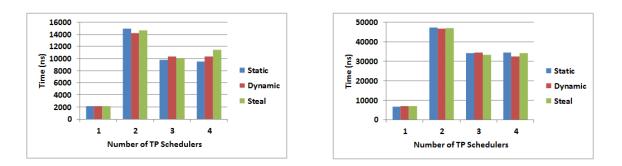

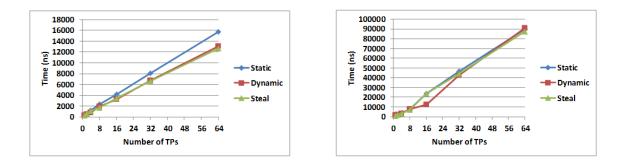

| 4.24 | TP Chain Pattern Running on Mills        | 78 |

| 4.25 | TP Chain Pattern Running on Monica       | 79 |

| 4.26 | Fully Strict Tree                        | 80 |

| 4.27 | Non-Strict Tree                          | 80 |

| 4.28 | Tree Pattern Running on Mills            | 81 |

| 4.29 | Tree Pattern Running on Monica           | 83 |

| 5.1  | DARTS' DGEMM                             | 85 |

| 5.2  | Weak Scaling of DGEMM                    | 86 |

| 5.3  | Strong Scaling of DGEMM Size 1000x1000   | 87 |

| 5.4  | Strong Scaling of DGEMM Size 10000x10000 | 87 |

| 5.5  | DARTS' Breadth First Search              | 89 |

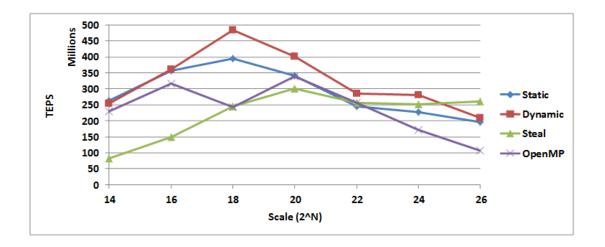

| 5.6  | Weak Scaling of Graph500's BFS           | 90 |

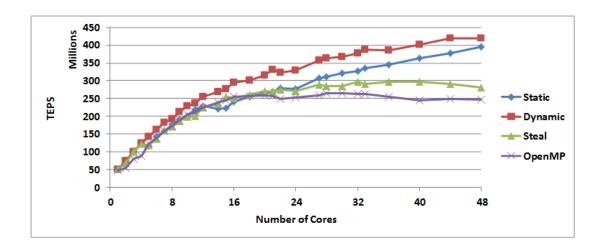

| 5.7 Strong Scaling of Graph500's BFS |  | 91 |

|--------------------------------------|--|----|

|--------------------------------------|--|----|

#### ABSTRACT

Over the past decade computer architectures have drastically evolved to circumnavigate prevailing physical limitations in chip technology. Energy consumption and heat expenditure have become the predominant concerns for architects and chip manufacturers. Previously anticipated trends such as frequency scaling, deep execution pipelines, and fully consistent caches in future many-core systems have been deemed unsustainable.

Current architectures are exhibiting new trends including simpler pipelines, lower frequencies, and scratch pad memories. Moreover, these architectures have an ever increasing number of cores. Many predict future architectures to contain thousands of heterogeneous cores on a single die.

With these radical shifts in architectures, current execution models are struggling to adequately scale in performance and newer metrics like energy consumption. The shortcomings of current models have caused some to look back to fine-grained execution models designed for parallelism like dataflow and EARTH. Using these models as inspiration, the Codelet execution model is an event-driven, fine-grained model designed to exploit parallelism while providing efficient mechanism for locality.

In the following, we present the Delaware Asynchronous RunTime System (DARTS), an implementation of the Codelet model. DARTS is a faithful implementation of the Codelet model, providing a vehicle to reason and further develop codelet ideas. It provides two levels of parallelism, event-driven codelets permitting fine-grained parallelism and invoked threaded procedures which ensures locality. Furthermore, the DARTS runtime is built on a reconfigurable abstract machine allowing DARTS to provide performance portability across both architectures and applications. In addition, we provide an in depth analysis of DARTS and its underlying model running on offthe-shelf hardware. Utilizing two x86 machines (both Intel and AMD), we explore the overheads of the codelet model and its implementation using micro benchmarks. Furthermore, we demonstrate DARTS' performance for two benchmarks, matrix multiply and breadth first search. Leveraging these results, we aim to establish the Codelet model as a promising execution model for future many-core architectures via an efficient and well-designed runtime. The following summarizes the contributions of this thesis:

- 1. A specification for the Codelet execution model

- 2. DARTS: An accurate implementation of the Codelet model

- (a) Two levels of parallelism; fine-grained tasks and procedures intertwined by fine-grain synchronization

- (b) Adaptable abstract machine capable scaling for different applications and hardware

- 3. A two phase evaluation of DARTS and the Codelet execution model running on available off-the-shelf hardware accomplish by

- (a) Micro benchmarking the base primitives employed by DARTS to realize the Codelet model

- (b) Evaluating case studies on selected benchmarks representative of workloads of interest including matrix multiply and breadth first search

## Chapter 1 INTRODUCTION

In order to further science, the high performance community is on an unending journey to achieving extraordinary levels of computing. Continuing in this effort, our next task is to achieve exa-scale performance. We face several daunting challenges requiring novel solutions in order to accomplish this goal. These challenges go beyond compute performance to achieving energy efficiency, resiliency, security, and more. The aim of this thesis is to provide an execution model and runtime to act as a platform for future research addressing these problems.

Historically, the use of an execution model, or program execution model (PXM), has become unfashionable leading to a schism between hardware and software architects. More recently however, this has changed due to the advent of the many-core era. In order to provide useful (and usable) systems, both hardware and software developers have realized the need for a unified view of the entire system. An execution model provides the abstraction and principles upon which the underlying system architecture and system software should be conceived, designed, and developed. The execution model provides the governing principles for the system design, operation, management, and application. This model is implemented not by any single component of a system; rather it is the sum of its parts. The execution model's reach spans the whole system, crosscutting all layers including the system architecture and software stack.

One crucial piece of an execution model's implementation is a runtime system. A runtime provides flexibility in satisfying a particular execution model's requirements by bridging the gap between software and hardware. This permits researchers to study different models on a single platform. The approach is not without caveats however. A runtime is only capable of satisfying certain hardware limitations. If the hardware does not provide sufficient mechanism to a runtime, certain features of an execution model may not be feasible. Furthermore, there are many trade-offs in deciding which features of an execution model should be in software (implemented in the runtime) or hardware.

Future exa-scale machines will have thousands of cores per node [5, 42]. Moreover, the physics of these systems (fabrication and operation) have brought new metrics like energy efficiency and resiliency to the forefront. It is unclear whether current models will be capable of scaling to the parallelism available in future large scale systems, and currently lack sufficient facilities to address these new metrics. As such, we believe now is the time for a new execution model.

An execution model suitable for exa-scale must be highly scalable, energy efficiency, and resiliency. The objective of this thesis is to propose an event-driven execution model. Event-driven execution goes beyond control-flow or dataflow to executing task based on *events*. We believe an event-driven execution model can sufficiently provide the mechanisms to tackle these challenges. Moreover we provide a means of exploring the model on current architectures using a runtime and several benchmarks. The following summarizes the contributions of this thesis:

- 1. A specification for the Codelet execution model, an event-driven, fine-grained, multi-threading model aimed at scaling to future large scale heterogeneous systems.

- 2. Delaware Adaptive RunTime System (DARTS), a codelet runtime for shared memory x86 systems.

- 3. A two phase evaluation of DARTS and the Codelet execution model via micro benchmarks and two case studies.

We begin by illustrating the shortcoming of current models and describing past execution models which paved the way for the Codelet model in chapter 2. Next we introduce the Codelet execution model in chapter 3. Chapter 4 presents DARTS and several micro benchmarks. We continue our codelet exploration in chapter 5 with two case studies. Lastly we present the related work in chapter 6 and conclude in chapter 7.

# Chapter 2

### BACKGROUND

Over the past several years, we have successfully entered the peta-scale era using execution models which have evolved from sequential computers. The principal execution model has been based on the the von Neumann model which is comprised of a serial process running in a linear address space controlled by a single program counter.

Parallelism has been introduced by adding multiple execution units (i.e. cores). One (possibly outdated) means of categorizing parallel machines has been to use Flynn's taxonomy. The parallel architectures included in the taxonomy are Single Instruction Multiple Data (SIMD), Multiple Instructions Single Data (MISD), and Multiple Instruction Multiple Data (MIMD). The most significant of these are SIMD and MIMD, and can be furthered decomposed beyond Flynn's taxonomy [22]. Parallel systems characterized by SIMD or MIMD can be a distributed memory system (one which is comprised of multiple address spaces requiring some form of message passing) or a shared memory system (one with only a single address space requiring coordinated synchronization operations).

The effects of many architectural trends are present in current parallel systems. For example many systems exhibit SIMD parallelism using SSE directives to take advantage of vector processing. Moreover, the SIMD idea has evolved to SIMT (Single Instruction Multiple Threads) popularized by NVIDIA's GPU accelerators [33]. Shared memory MIMD systems leverage parallelism through some form of threading. The most popular are the OpenMP and POSIX threading models. Distributed memory MIMD systems primarily use MPI to coordinate the execution of processors operating in distinct memory addresses. It is common to find some combination if not all of these parallel features in the today's fastest large scale systems (e.g. a system using MPI for inter-node communication and OpenMP for intra-node communication). Today's parallel systems are already heterogeneous exploiting various forms of parallelism. Future architectures are expected to continue this trend while exposing even greater amounts of parallelism to the programmer.

Knowing the scale of future architectures, many are searching for more effective means of combining both inter-node and intra-node parallelism. This task has proven quite difficult, and often requires significant rewriting of application code and a high level of programmer expertise [12]. Despite this trend many are clinging to current execution models, in hopes to maintain their application investments (time, code, money, and tool-chain). As such, these parties seek an evolutionary path to exa-scale. This approach has been deemed the MPI + X where X is preferably OpenMP [1]. This approach faces several challenges.

OpenMP was first released in 1997, and is supported by most modern compilers [40]. OpenMP is a standard which extends the C languages with pragma based directives supporting thread parallelism. Prior to 2004, OpenMP has been centered on leveraging loop parallelism in a fork/join execution model. More recently, OpenMP has extended the standard to include asynchronous tasks.

The OpenMP model has previously focused on exploiting loop parallelism, dividing iteration into chunks. Different policies are used to determine the way in which chunks are distributed to threads. One problem encountered with this approach is how parallelism is expressed and thusly executed. Loop based parallelism leveraging a fork/join model can easily lead to system load-imbalance (where resources, primarily compute elements, are underutilized). This happens when chunks (or iterations) are not uniform (requiring varying amounts of time to execute). In these instances, threads are stalled at join points waiting for the remaining threads to finish, leading to underutilization.

The uniformity of work per iteration is primarily application dependent. However, the latency of memory accesses and other contended hardware resources can cause non-uniformity in even regular applications [26]. Non-Uniform Memory Access (NUMA) effects have been caused by the movement of the memory controller onto the same die as the CPU [34]. Multiple cores with multiple memory controllers make up a single address space via a point to point network, and a cache coherent protocol enables access to remote memory. Accessing memory attached to a processor clearly has a lower latency then accessing data through the network. The differing latencies of memory accesses can lead to very different execution times for OpenMP chunks. Moreover, we find that compute elements are fighting for shared resources like network bandwidth and floating point units. Both of these trends are leading to less uniformity in applications.

To mitigate these issues many are exploring asynchronous tasks including OpenMP. Unfortunately, many, including OpenMP, limit their exploration of tasks based on control-flow (as opposed to dataflow based execution). The dataflow model conveniently decomposes a problem to show the maximum parallelism in an application [2] which will be important for mapping applications to future systems.

Another important issue facing the MPI + X approach is the poor (or nonexistent) interaction between the two distinct models. An unsatisfactory approach to combining these two models is to use two separate runtimes. This may lead to message buffers (within the runtimes) to be physically far (in the memory hierarchy) from producing and consuming threads leading to an increase in energy consumption as data must be moved [1]. A more satisfactory approach is explored in MPC [39], where both MPI and OpenMP standards are implemented in a single runtime. Unfortunately, despite a unified runtime, leveraging MPIs standard tends to forces workloads to be statically partition across nodes [32]. A unified model will be better poised to loadbalance an entire system, ensuring efficient resource utilization. Moreover, an execution model for exa-scale must balance parallelism with locality to stay within an acceptable power budget. Addressing these issues in two separate but joined models is a daunting challenge.

To overcome these issues a unified, event-driven, fine-grained execution model

is needed. The required model's implementation should have low overhead (in order to scale), and permit fine-grain parallelism all while ensuring locality. Moreover, the model must embrace the heterogeneous resources available in future systems. The remainder of this section describes the path leading up to the Codelet execution model, a disruptive technology intended for exa-scale performance. We begin in section 2.1 by describing dataflow in several flavors and the EARTH execution model in 2.2.

#### 2.1 Dataflow

The Codelet model's deepest roots lie in the dataflow model of computation. Dataflow provides several important features including fine-grain synchronization, functional programming, composability, and determinate execution [46]. Most importantly, dataflow exposes the maximum amount of parallelism available in a given program [2]. In order for an execution model to scale to an architecture with a larger number of cores, it must expose and exploit sufficient parallelism in underlying programs to fully utilize the system. For this reason, the dataflow model serves as a solid foundation for the exploration of an exa-scale capable execution model.

#### 2.1.1 Static Dataflow

In the early 1970's, Jack Dennis proposed the first version of the dataflow model, later dubbed static dataflow [18, 19]. The dataflow model takes a radically different approach to organizing and executing instructions. Rather than expressing a program in a series of sequential instructions, programs are represented by graphs.

#### 2.1.1.1 Dataflow Graphs

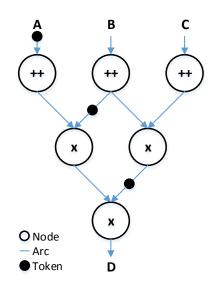

In dataflow, computation is modeled as a DataFlow Graph (DFG). A DFG is a directed graph consisting of nodes, arcs, and tokens [13, 31]. The following is a description of each component of a DFG:

Actor is a node which represents an operation to be performed on a piece or pieces of data. An actor will take one or more inputs, perform the specified operation, and provide data to its outputs.

**Arc** represents a data dependency between actors. Arcs signify the passing of data from one actor to the next, primarily representing a producer/consumer relationship.

Token represents data traveling on an arc between actors.

Figure 2.1: A DataFlow Graph (DFG) contains actors, arcs, and tokens.

#### 2.1.1.2 Operational Semantics

Tokens passed from one actor to the next are used to signify the presence of data. The directed arcs represent the data dependencies between actors. An actor fires, or executes its operation, based on the following rule [19]:

General Firing Rule: An actor becomes enabled when a token is present on each of its input arcs. An actor then fires by consuming the input tokens, performing its operation, and placing a token, the result of the operation, on each of its output arcs.

As each actor fires, the execution of the dataflow program is progressed. Each individual actor has no internal state since the operation it represents is of the finest granularity. The state of the application instead is found in the entire DFG. A snapshot of a DFG shows tokens traveling from actor to actor across arcs during execution. Thus, the state of a dataflow program is the sum of its actors, arcs, and tokens for a given snapshot.

Multiple actors are permitted to fire as long as the firing rule for each individual actor is met (since DFGs have no concept of the hardware executing them). This is the way in which parallelism is expressed; asynchronous actors are only bound by their inputs and execute concurrently. Moreover, since each actor is only a single operation limited only by its inputs, we see a DFG permits the finest granularity of parallelism.

#### 2.1.1.3 Limits of Static Dataflow

Static dataflow differs from other incarnations of the dataflow model based on one simple restriction of the general firing rule. In static dataflow, an actor may only fire when all of its input tokens are available and all of its output arcs are empty. This important distinction lends the bases for static dataflow's other name, single-token-perarc dataflow as ensuring output arcs' freedom before firing limits all arcs to containing at most one token. To ensure this property, network traffic is effectively doubled since actors must signal their preceding actors that their output arcs are free [4, 46]. This inefficiency led to the development of the dynamic dataflow model.

#### 2.1.2 Dynamic Dataflow

Dynamic dataflow, also known as tagged-token dataflow builds on static dataflow addressing the overhead caused by the only permitting a single-token-per-arc [3, 48]. In dynamic dataflow, each token is augmented with a color which is used to determine for which instruction the data value is destined and additional contextual information used to determine which other tokens should be used when the instruction fires. By "tagging" tokens with a color, multiple tokens may reside on a single arc with a modification to the firing rule.

**Tagged-token Firing Rule:** An actor becomes enabled when tokens with corresponding colors arrive on all of its input arcs. The actor fires by removing the colored

tokens from its input arcs, executes the instruction, and places the result on its output arc with an appropriate color.

With multiple tokens per arc, data can be reordered as long as the firing rule is observed providing better performance. The trade-off of tagging tokens is the time required to match tokens. Depending on the operation and the number of tokens on an arc, locating matching tokens might be more costly than performing the actor's operation. For this reason, a fully associative memory is ideal for reducing the latency of token matching. Unfortunately a required associative memory is impractical due to its size. One alternative to overcoming this challenge is to use hashing techniques [46]. A more satisfactory method is to employ the explicit token store technique [36]. Token matching becomes extremely expensive when executing loops in dynamic dataflow since iterations may execute out of order. The explicit token store alleviates this burden by assigning each active iteration a frame. Actors leverage explicit token store by using a frame and offset to store and access each token.

#### 2.1.3 Argument Fetching

One limitation of the previously mentioned forms of dataflow is excess storage and the network traffic required to copy operands. Argument-fetching dataflow attempts to address this shortcoming by dissociating the signal and data sent to consuming actors [23]. Alternatively, each actor contains an instruction, addresses to its arguments, an address to the result, addresses of actors to signal, an enable count, and a reset count. When an actor is fired, its arguments are read from memory and the result is written to memory. When the instruction is finished, the proceeding actors are signaled decrementing their enable count. Once the enable count reaches zero, an actor is fired, after which the counter is reset. By disassociating the signal and the data, the result only needs to be written and stored once. This trades time for space, as the latency of accessing arguments is increased.

#### 2.2 EARTH

While dataflow exposes the maximum parallelism found in an application, it is still plagued with several drawbacks. One primary weakness of dataflow is the high cumulative overheads resulting from fine-grained synchronization. These costs may include reading and writing operands, signaling, and locating and executing enabled actors. Moreover these overheads are exacerbated when running a sequential code, where a von Neumann counterpart excels. Dataflow also fails to effectively take advantage of locality, which is a primary concern for future architectures as data movement dominates the energy consumption of a machine. Due to these limitations, hybrid von Neumann/dataflow architectures have been developed.

One such model is the Efficient Architecture for Running Threads (EARTH) designed in the late 90s. EARTH's goal was to provide a simple, efficient, and evolutionary execution model to enabling the construction of a full scale multiprocessor utilizing commodity hardware. The following is a summarization of work done by Theobald [45], Hendren [28], and Hum [29].

#### 2.2.1 EARTH Threading Model

EARTH attempts to take advantage of many ideas set forth by dataflow while addressing issues such as the lack of locality found in a DFG. The EARTH thread model is hierarchical containing two levels of threading, fibers and threaded procedures.

#### 2.2.1.1 Fibers

Fibers are asynchronous, non-preemptive, sequences of instructions. Each fiber has a synchronization slot which determines when a fiber fires. A synchronization slot contains a counter and the number of dependencies needed to fire a fiber. A fiber is executed based on the following firing rule:

**Fiber Firing Rule:** A synchronization counter is set to the number of dependencies required. Once the counter reaches zero, all dependencies have been satisfied enabling the fiber. The fiber may fire once a processing element is available.

Fibers are connected through their data dependencies forming a graph similar to a DFG. Parallel execution of fibers is permitted given each fiber is enabled and processors are available.

#### 2.2.1.2 Threaded Procedures

Threaded procedures combine ideas from both explicit token storage and argument fetching dataflow. A threaded procedure contains at least one fiber, the local variables shared between fibers, and parameters passed to the procedure. Fibers and threaded procedures are tightly coupled, as each fiber must belong to a single threaded procedure. Threaded procedures are invoked by running fibers (except for an initial procedure). Every threaded procedure has at least one fiber, called fiber 0, which is the first in the procedure to fire. Fibers contained within the threaded procedure may produce data and signals for fibers both contained within and outside their own threaded procedure. A threaded procedure is maintained in memory until a fiber terminates the procedure, causing its deallocation including the procedure's fibers and data. The EARTH model takes advantage of two levels of parallelism; threaded procedures execute in parallel as well as the fibers they contain.

#### 2.2.2 EARTH Architecture Model

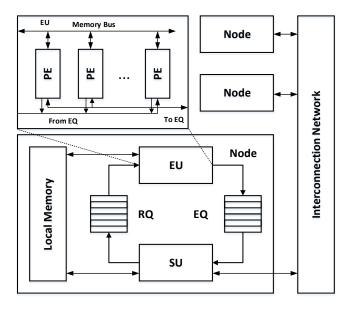

Since EARTH has played an important role in developing the Codelet model, it is useful to look beyond its threading model to its architecture model. The EARTH architecture model demonstrates the structure and organization of an abstract machine capable of supporting the threading model. An EARTH system is comprised of at least one EARTH node connected by some network. An EARTH node is made up of the following components:

- Execution Unit (EU) May contain one or more processing elements (cores or threading units) and is responsible for executing fibers

- Synchronization Unit (SU) A processing element responsible for synchronizing fibers and threaded procedures as well as handling remote data accesses.

- Event Queue (EQ) A queue containing operations produced by the EU for the SU to execute.

- Ready Queue (RQ) A queue of fibers which are ready to be executed

Figure 2.2: The EARTH architecture model describes physical components and their configuration required to run the threading model.

An EARTH node's EU and SU communicate through two queues, the EQ and RQ. As fibers are executed in the EU, they produce synchronizing instructions (e.g. satisfying another fiber's dependency). The SU is responsible for decrementing the synchronization slot of other fibers and writing remote data. This separation of task was intended to address the long latency and limited bandwidth of commodity processors available in the 90's. By decoupling the synchronization from execution, the EU is not required to suspend execution. Traditionally, this problem is handled through preemption; however this requires either register windows or pushing and pulling execution contexts to and from slower memory.

#### 2.2.3 EARTH's Advantages

The EARTH model was designed to explore dataflow based multiprocessing in an evolutionary manner via off-the-shelf hardware available at its inception. Despite being designed before the commonplace of multi- and many-core architectures, its creators provided several innovations meaningful for today and future architectures.

An important advancement is the hierarchical expression of parallelism provided by the programmer. Relying on dataflow semantics, both fibers and threaded procedures may run in parallel. By grouping fibers together, programmers are capable of expressing both a fine-grained parallelism encompassed in a more familiar functionlike wrapper. While, fibers are intended to run in parallel, an EU was typically a single processor (at the inception of the EARTH model). EARTH's architecture model permitted the exploration of multi-threaded execution without actual multi-core technology. With the advent of multi- and many-core, hierarchical threading has much more significance.

Another important development is EARTH's balance between parallelism and locality. While EARTH explores dataflow inspired parallel execution, it does so at a macro-dataflow level, providing the exploitation of temporal and spatial locality found in traditional von Neumann architectures. Moreover, the grouping of fibers in threaded procedures provides a means for sharing data leading to more locality.

The Codelet model builds on these contributions, further discussing them in many-core context in following chapter.

## Chapter 3 CODELET MODEL

The previous chapter describes several parallel execution models, all developed before the multi- and many-core era. These models primarily focus on the exploitation of fine-grain parallelism. As we look forward to exa-scale, we are forced to address the pressing energy constraints imposed by the physical world. In doing so, parallelism must effectively be balanced with locality and tailored to the large scale heterogeneous machines of tomorrow. A philosophical document has outlined our initial views of a Codelet model [25]. The following chapter proposes an updated specification reflecting our experience working with several codelet based runtimes. The Codelet model is a hybrid von Neumann/dataflow execution model [50, 44]. The model is a means to develop the underlying system architecture and system software for exa-scale computing. Based on a configurable abstract machine model, the Codelet model extends fine-grain multi-threading to provide facilities to address resource utilization including locality. The current chapter discusses the abstract machine model in section 3.1. Section 3.2 presents the threading model followed by the Codelet architecture model presented in section 3.3.

#### 3.1 Codelet Abstract Machine Model

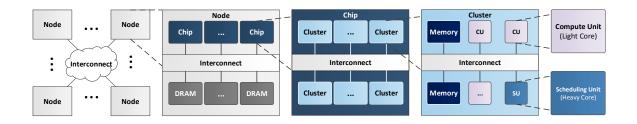

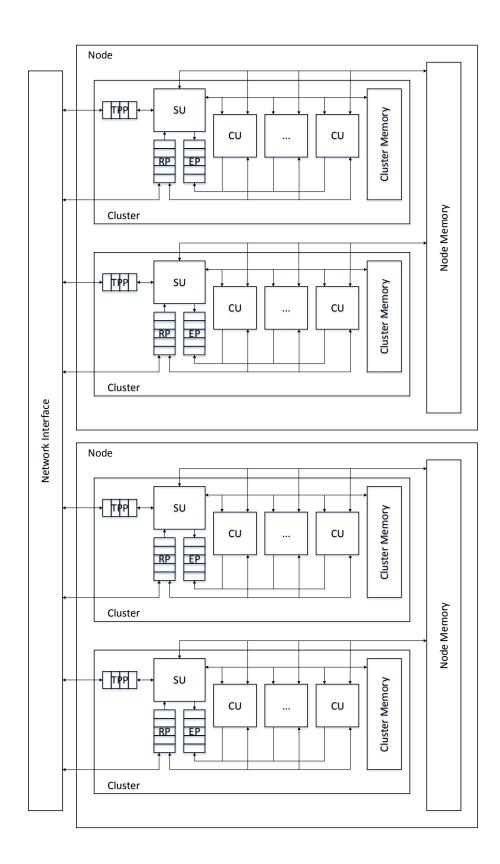

In conceiving an execution model for exa-scale, it is imperative to consider the characteristics of current and future many-core systems. For that reason we present the abstract machine model, a representation of the type of system well suited for the Codelet model. The figure 3.1 depicts our view of future many-core systems.

The codelet abstract machine model consists of many nodes connected together via some interconnection network. Contained within a single node are multiple chips,

Figure 3.1: The codelet abstract machine is hierarchical and heterogeneous. Moreover, the machine will be extremely parallel and with various levels of memory (each with different latencies).

each with DRAM memory coupled by some interconnect. Within a chip exists groups of heterogeneous cores with both shared memory and local memory, called clusters. We envision two types of cores:

- Computation unit A core specialized for executing codelets (e.g. sufficient for executing general purpose code). This core is connected with other computation units within its cluster, but lacks access to remote memory or IOs.

- Synchronization unit A core responsible for servicing events (signaling codelets) and load balancing codelets and TPs. This core has access to remote memory and IOs.

We believe that this high level view is specific enough to provide a solid foundation for the Codelet model. In summary a codelet capable system will have the following properties:

- Parallel These systems will have plenty of compute resources available.

- Hierarchical The system must be hierarchical to effectively manage the compute resources available to the programmer.

- NUMA Interconnects binding components at several levels will have varying latencies.

- Heterogeneous Different cores will be specialized for different tasks like computation intensive cores and synchronization cores.

#### 3.2 Threading Model

The threading model details how parallel programs are expressed in a parallel system. The Codelet model employs hierarchical, fine-grained, event-driven multithreading. The model is designed to explore parallelism to sufficiently utilize a large scale systems, while still providing mechanism to ensure locality. Striking the right balance between parallelism and locality is paramount in achieving an energy efficient system.

#### 3.2.1 Codelet

The Codelet execution model is centered on the concept of a codelet. A codelet is a sequence of machine instructions. A codelet is the principal scheduling quantum in the model as it is scheduled atomically. In order to better utilize the underlying system, codelets are event-driven. Each codelet has an event synchronization slot which represents the dependencies required by the codelet before it may execute. The most common event is the availability of data (i.e. satisfaction of a data dependency); however it is not limited to this alone. Events include the following:

- Data dependencies A codelet may require specific data produced by another codelet

- Control dependencies A codelet may signal another codelet based on some condition similarly to a dataflow control actor [19]. Doing so may change the execution path of a CDG enabling certain codelets while disregarding others.

- Locality dependencies A codelet may prefetch data for other codelets to use concurrently. This differs from the data dependence since the event is used to indicate the location of the data in memory.

- Energy events Different functionally equivalent codelets may have different performance versus energy trade-offs. Energy events could decide which codelets to execute.

- Other resource requirements (e.g. bandwidth, network, etc.)

A codelet is executed, or fired, based on the following rule:

**Codelet Firing Rule:** Each codelet's synchronization slot is used to keep track of the events required prior to codelet execution. When all of a codelet's event have occurred,

the codelet becomes enabled. Once a processing element (core) is available, the codelet may be fired.

As each codelet is executed, it satisfies events required by other codelets. A codelet's output is not atomic, meaning it may satisfy an event and continue running. This is contrary to traditional dataflow semantics which complete an actor's execution before signaling. This provides a more natural overlapping of codelet capable of executing in parallel. Enabled codelets may execute in parallel since all of their events (i.e. dependencies) have been satisfied.

Codelets are very similar to EARTH's fibers. The main difference being codelets are event driven versus data driven fibers. This distinction is important for future architectures as events generated from an intelligent runtime or hardware units may shape the execution of an application. By generalizing signaling, we provide the facilities for future work in areas such as energy management and resiliency.

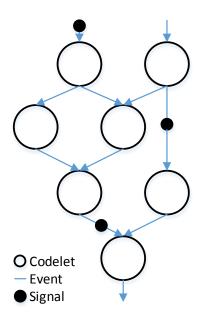

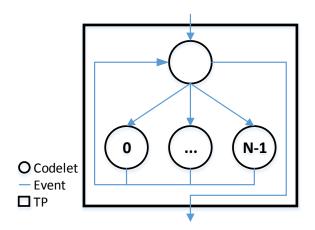

#### 3.2.2 Codelet Graph

Connecting codelets and their dependencies via events naturally form a graph similar to a dataflow graph. This interweaving of codelets is called a CoDelet Graph (CDG), and is useful for reasoning about a given application. A CDG is a directed graph consisting of three components:

**Codelet** Represented by a node, indicate a sequence operations to be performed.

- **Event** Represented by an arc. The arcs entering or exiting a node indicate a potential signal from a codelet representing an event.

- Token Represented by a point on an arc indicating a signal.

The CDG is a very effective mechanism to observe the available parallelism in a given application. By studying the CDG, one can locate regions of an application containing both plentiful and sparse amounts of parallelism.

Figure 3.2: A CoDelet graph (CDG) contains codelets, events, and tokens.

#### 3.2.3 The Ideal Codelet

The codelet model proposes a method of expressing programs foreign to many programmers. Furthermore, there are (efficient) solutions to some challenges presented by applications which would not be possible in a dataflow system. To not exclude these solutions as they could present a more optimal approach, the Codelet model permits certain caveats to the ideals of the model at the programmer's risk. The following presents the "ideal codelet." Breaking these ideals does not necessarily imply an incorrect program, but it may negate certain properties such as determinate execution.

#### 3.2.3.1 Non-Preemptive

Similar to the EARTH model, codelets should be not be preemptable. Today's traditional multi-threaded systems may suspend execution of a thread due to some external event. This requires the context of the thread including the thread's frame and registers be swapped with another thread. This is costly in both time and energy, as moving data is expensive. Codelets should be fine-grained enough to permit it to run to completion.

Moreover, some systems use the same methodology to tolerate long latency operations executed by a thread. This "voluntary yielding" is not appropriate for the Codelet model as codelets should have all data and resources required locally before firing. In ensuring the availability of resources before execution, a codelet will not need to be suspended as the operations will have short latencies. However, an architectures with features like register windows might not suffer the same costs in time and energy switching between windows. In this type of system, yielding might be a reasonable concession.

Another technique capable of mitigating effects of long latency operations is to use split-phase transactions. A split-phase transaction divides a single codelet containing a long latency operation. The first codelet ends after initiating the operations. One or more codelets will continue after it is complete (and the continuing codelets have been signaled). Dividing the codelet permits the computation unit an opportunity to fire other enabled codelets while the long latency operation is still outstanding.

#### 3.2.3.2 Well-Behaved CDGs

The dataflow model can provides strong guarantees like determinate and repeatable execution [20]. These properties emanate from well-behaved schemata [19] and side-effect free actors.

An actor is well-behaved if and only if an actor consumes all of its input tokens (one for each input arc), and produces an output token for each output arc. An acyclic, simple dataflow graph (e.g. a graph without control gates or merge nodes) is determinate [19, 37]. Assuming a codelet is side-effect free, a codelet is similarly well-behaved if and only if each possible input *data event* occurs, and the codelet fires signaling all of its output *data events*. Moreover, an acyclic combination of these determinate codelets form a determinate CDG.

#### 3.2.3.3 Well-Formed CDGs

Traditional dataflow contains non-well-behaved actors used to implement controlflow. These actors include a switch, merge, and true and false gates. Using the construction rules provided in [19], these actors can be used to create well-formed graphs. A well-formed graph is also a well-behaved graph, however the contrary is not always true.

Argument-fetching dataflow modifies the dataflow graphs to a signal graph by separating data from the signaling of actors. Signal graphs do not fire switch or merge actors. Rather, the same functionality is achieved by properly linking the nodes in a graph and conditionally signaling consuming nodes as shown in [14]. The Codelet model follows this approach in implementing conditional statements.

More recently, a homogeneous form of dataflow has demonstrated the same properties exhibited by traditional dataflow [47]. This approach requires static dataflow semantics. That is, an actor must not be capable of firing until its output links are free. The actors proposed are analogous to the nodes in the signal graph and also codelets in a CDG. To leverage the proof from homogeneous dataflow, the Codelet model must also observe static dataflow's single-token-per-arc rule. Multiple tokens on an arc originate from either loops, recursive function invocations, or streaming data.

In order to support recursive function invocations and parallel for loops, a CDG is duplicated (using Threaded Procedures proposed in section 3.2.4) and linked appropriately avoiding multiple tokens per arch. Current research is being conducted to determine how best to support streams.

#### 3.2.4 Threaded Procedure

Similar to the EARTH model, asynchronous functions are called Threaded Procedures (TPs) in the Codelet model. Much like its ancestor, the codelet model's TPs are containers for a CDG. A TP also features a frame which holds the inputs passed to it, the resulting output, and data shared by the contained codelets. TPs are invoked (like a function call), and exist in memory until all of the codelets in the CDG have finished executing. By grouping all of the codelets and necessary data together, a TP provides a convenient mechanism for codelets to access data and other codelets (important for signaling events). A TP and its codelets are confined to a single cluster and residing in cluster memory ensuring locality.

#### 3.2.5 Loop

A loop in the codelet model is represented by a cycle in a CDG. That is the loop body is comprised of several codelets. There are two forms of loop parallelism exploited in the codelet execution model. The first and simplest is *parallel for* loops. These kinds of loop do not have any loop-carried dependencies permitting the iterations to run in parallel. The second form of loop parallelism is codelet software pipelining. Current research is being conducted to determine how to utilize software pipeline for the Codelet model [49].

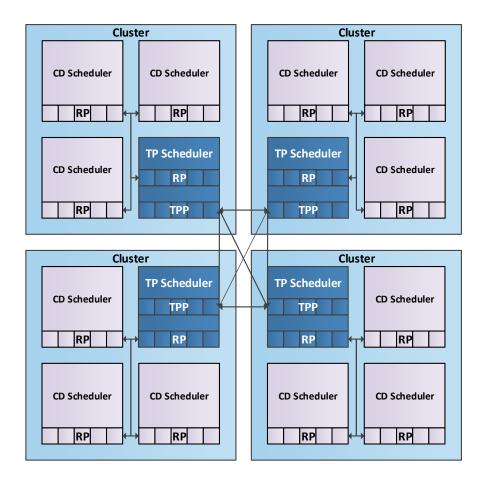

#### 3.3 Codelet Architecture Model

The previous sections detailed the abstract machine model and the threading model. The following describes how the threading model is mapped to the abstract machine model. The Codelet architecture model describes the responsibility of the components that comprise a system capable of exploiting the Codelet model.

The abstract machine outlines a hierarchical system including nodes, clusters, synchronization units, and computation units. The Codelet architecture model includes three queues in addition to the component in the abstract machine model. These components are as follows:

- Synchronization Unit (SU)

- Computation Unit (CU)

- Threaded Procedure Pool (TPP)

- Codelet Ready Pool (RP)

- Event Pool (EP)

Figure 3.3: Codelet architecture model depicting two nodes with two clusters each.

#### 3.3.1 Synchronization Unit

The synchronization unit has several responsibilities including the distribution and synchronizing of the execution of codelets across clusters and nodes. The SU's primary responsibility is to load balance TPs both within and outside a node. TPs are claimed by a SU via the TPP. Once acquired, a TP's codelets are bound to the cluster. The TP's context (codelets and frame) are pushed into cluster memory, and the enabled codelets are pushed to the RP. Lastly, the SU synchronizes codelets outside of the cluster by servicing requests from the EP.

A SU will claim a TP based on the load of codelets already executing on its cluster. If the cluster has no codelets running, the SU will try to claim a TP from its own TPP. If there are no TPs available in the TPP, the SU will attempt to claim TPs from neighboring clusters in a work stealing fashion. A SU may try to buffer codelets by claiming TPs while other codelets are still running on its cluster. This is considered part of the SU's scheduling policy and is part of a particular codelet implementation. One example of a SU's scheduling policy is to try to maintain a certain amount of codelets ready to run in the RP.

#### 3.3.2 Computation Unit

The computation units are responsible for executing codelets which make up an application. Several CUs are grouped together to form a cluster. A CU has access to all of the memory contained in the node including cluster and node memory. Codelets are acquired from the RP by the CUs. CUs are responsible for directly signaling codelets which are local to the cluster. Once a codelet is enabled, it is placed in the RP where it waits for an available CU. If a codelet resides outside its cluster, the executing CU generates an event request and places it in the EP. When an enabled codelet is fired by a CU, its execution continues until the codelet is complete (its execution is not moved between CUs).

#### 3.3.3 Pools

There are three pools in the Codelet architecture model which serve as the glue between the event and codelet executing components, the Threaded Procedure Pool (TPP), Ready Pool (RP), and the Event Pool (EP). Each cluster contains these three pools.

The TPP holds the threaded procedures available which have not begun execution. When a running codelet invokes a TP, the TP is immediately placed into the TPP. SUs are responsible for claiming TPs from the TPP based on the SU's scheduling policy.

The RP contains all of the enabled codelets which are ready to run in a cluster. The RP is accessed by both the SU and the CUs within a cluster. When a TP is claimed, the SU will place the enabled codelets into the RP beginning the TP's execution. The codelets placed in the RP by the SU are codelets that do not require any event to fire. Codelet that are not enabled exist in memory local to the cluster. Once these codelets become enabled, they are placed into the correct RP by the CU or SU responsible for enabling them.

Signals that satisfy an event outside of a codelet's cluster generate an event request, which is placed in the EP. The SU accesses the EP, and satisfies the event's request potentially enabling codelets outside of the cluster.

# **3.3.4** Memory and Interconnect

A complete memory model is comprised of an addressing mode and memory consistency model. A memory model's purpose is to provide an agreement on the semantics of memory operations between hardware and software to ensure proper execution of the user's program.

The previously mentioned philosophical document proposes a codelet architecture with a Location Consistency (LC) based memory consistency model [25]. LC is a sufficiently weak model which respects causality. In LC, the content of a memory location is not a monolithic value, but rather a partially ordered multi-set (POMSET). Operations (read, write, acquire, and release) to the POMSET are defined by Gao and Sarkar [24]. A memory consistency model is enforced (primarily) by physical hardware. Memory consistency models like sequential consistency permit a narrow view of memory, forcing hardware to synchronize (potentially unnecessarily). This synchronization is not only costly in time, but also energy. This motivates our recommendation for LC as a strong candidate for future systems.

Another possible scenario is for codelets to leverage a write-once policy. Under this policy, codelets would not "release" produced data until their completion. This idea is explored further in [17].

The appropriate addressing mode of a codelet based system is still under investigation. One potential idea is the use of Globally Unique Identifiers (GUIDS). GUIDS would be assigned to codelets and TPs providing a unique name (address) permitting access across distinct memories (i.e. distribute memory systems).

The codelet threading model only requires an atomic decrement used to decrease the synchronization slot. Additional atomic operations, like the popular compare-andswap are not required, but helpful in designing efficient data structures used in a codelet runtime. Furthermore, the Codelet architecture model does not require a particular topology for the interconnection network. By limiting the demands of the Codelet model, it may be implemented on a wider variety of systems.

# Chapter 4 DARTS

While an execution model is implemented via an entire system, a runtime can augment hardware not designed for a particular model. The Delaware RunTime System (DARTS) is a runtime written for shared memory x86 architectures to implement the Codelet execution model. While there are other codelet based runtimes [32, 15], DARTS attempts to remain as accurate as possible to the aforementioned model with the intent of analyzing and further developing codelets. DARTS is written in C++, and takes advantage of object oriented programming. Using C++ is low level enough to provide sufficient control over the underlying hardware while still promoting modularity and portability. The following is the description of the DARTS implementation and an evaluation using micro benchmarks.

# 4.1 Implementation

The codelet threading model is comprised of three elements, codelets, TPs, and loops, which are implemented as C++ objects. Each object uses inheritance and virtual functions to define a particular instance of the type of object.

# 4.1.1 Codelets

Codelets are the core of a DARTS application, and are derived from a base class called Codelet. The base codelet class has several important fields including a synchronization slot, reference to a TP, and some space for metadata. The synchronization slot stores the total number of events required to fire, and a counter. The counter is set to the requisite number of events and is decremented until it reaches zero which enables the codelet. Once a codelet is enabled, it is ready to execute using the virtual fire method which contains the codelet code. The fire method is a pure virtual method defined in the base codelet class and implemented in a inherited class specialized by the application programmer. While the fire method is executing, it has access to the codelet's TP reference enabling it to access data and other codelets in the TP. Moreover, the metadata associated with a codelet permits additional information useful for scheduling as demonstrated in section 4.2.1.4.1.

A codelet has four input parameters which directly correspond to its members. A specialized codelet must provide the number of requisite events, a reset event count, a reference to its TP, and metadata to the base classes constructor. A codelet may access its TP reference via the myTP<sub>-</sub> member. The following is an example codelet.

```

#include <iostream>

#include ''darts.h''

2

using namespace darts;

3

4

class SomeCodelet : public Codelet

{

6

public:

7

SomeCodelet (uint32_t EventCount, uint32_t EventReset,

8

ThreadedProcedure * TPReference, uint32_t Metadata):

Codelet(EventCount, EventReset, TPreference, Metadata) { }

9

virtual void fire(void)

11

12

{

std::cout << ``I am a codelet from `` << myTP_ << ``!`` << std::</pre>

13

endl;

}

14

};

15

```

# 4.1.2 Threaded Procedures

TPs are designed to be containers for codelets and shared data. As such, a TP inherits from a base class called ThreadedProcedure, and is extended with data and codelets. A typical TP contains references to input data, internally shared data (between codelets), output, codelets, and a reference to codelets to signal outside of the TP. Codelets using their TP reference are capable of writing and reading shared data. During the TP's construction any enabled codelets should be passed using the add method. The add method takes a reference to a codelet and passes the codelet to the runtime to begin its execution. The following is an example TP.

```

#include <iostream>

#include ''darts.h''

2

using namespace darts;

3

4

class SomeTP : public ThreadedProcedure

{

6

public:

int x, y;

8

int * result;

9

CodeletOne cd1;

10

CodeletTwo cd2;

11

Codelet * toSignal;

12

13

SomeTP(int * Result, Codelet * ToSignal):

14

ThreadedProcedure(),

result(Result),

16

toSignal(ToSignal),

cd1(0, 0, this, 0),

18

cd2(2, 2, this, 0),

19

toSignal(ToSignal)

20

{

21

add(&cd1);

22

}

23

};

24

```

TPs and all of their members are allocated on the heap. DARTS employs a reference count based garbage collection to automatically delete TPs when they are no longer needed. A simple counter is used to keep track of the number of outstanding enabled codelets and children TPs (TPs that have been invoked by contained codelets). This ensures that all of a TP's executing codelets have access to the data residing in the TP as well as codelets from children TPs. Once a TP's reference count reaches zero, it will decrement its parent TP, and the TP will be deleted. It is necessary to include children TPs in the reference count since a TP may have invoked its child TP performing a split-phase transaction. During this time it is possible there will be no codelets running from the parent TP. In this case the parent TP would be deleted leading to a fault.

This method of garbage collection is sufficient for most codelet applications, however not for all. If an application requires data to persist past the execution of its codelets, the data, if stored in the TP, should not be deleted until specified by the programmer. For this reason, methods are available to the programmer to artificially increase and decrease the reference count ensuring the TP will remain in memory for as long as desired.

# 4.1.3 Loops

DARTS implements three types of loops, a serial loop, a codelet for all loop, and a TP for all loop. These loops give the programmer the flexibility to decide to some degree where parallel iterations will be executed, whether it be on a single core, single cluster, or the entire system. This allows the programmer to explore the trade-off parallelism versus locality.

Loops in DARTS are implemented in two parts, a specialized loop class and a control codelet. Specialized loop classes inherit from a base class called Loop. The base Loop class has two members, an iteration id and codelet to signal when the loop is finished. The specialized Loop class is comprised of a CDG and the data shared by the contained codelets. Codelets without any event requirements are passed to the runtime during the loops construction identically as TP's enabled codelets. The following is an example of the loop base class.

```

#include <iostream>

#include ''darts.h''

2

using namespace darts;

3

class SpecialLoop : public Loop

4

{

public:

int x, y;

7

CodeletOne cd1;

8

CodeletTwo cd2;

9

10

SpecialLoop(unsigned int Id, Codelet * ToSignal):

11

loop(Id, ToSignal),

12

cd1(0, 0, this, 0),

13

cd2(1, 1, this, 0)

14

{

add(&cd1);

16

}

17

};

18

```

The second part of a loop in DARTS is the loop controlling codelet. Leveraging C++'s templating, we implement three controlling codelets, the serial loop, the codelet for all loop, and the parallel for all loop.

# 4.1.3.1 Serial loop

A serial loop will loop over a CDG for a given number of iterations sequentially in a single cluster. This is not to say that all the codelets in the CDG are executed sequentially, rather that each iteration of the CDG is executed in order. A serial loop takes a derived loop type as its first template parameter, and allocates a single copy of the CDG on the heap. The serial loop object is implemented as a special codelet which is responsible for starting and stopping the loop. When this special codelet is constructed (during TP construction time) the loop CDG is allocated and the iteration id is set to zero. Once the serial loop codelet's synchronization counter reaches zero, the loop body begins execution. When an iteration is completed, the serial loop codelet is again signaled (transparently to the programmer). If there are still iterations remaining to be executed, the loop's iteration id is incremented, and the loop is reconstructed using C++'s in place allocator permitting the next iteration to begin. When all iterations are completed, the serial loop codelet signals its completion to the subsequent codelet provided at construction time.

The serial loop codelet takes at least three parameters:

- A number of requisite events to start the loop

- The number of events (signals from codelets contained in the loop) to end an iteration

- A codelet to signal once the loop is completed

- Number of iterations to perform

The CDG contained in the loop body will most likely require additional data beyond the loop construct's arguments. To pass this data into the loop's CDG, the data (as parameters) are appended onto the loop class' constructor method. The data can then be passed to the serial loop codelet's constructor (after the required parameters) in the order they appear in the loop constructor. The types of the additional inputs can be inferred by most modern compilers. Alternatively, one can pass the types of the additional inputs as template parameters after the loop type to the serial codelet. The inputs to the loop are stored and provided by the runtime during the loop's construction. As such, they are fixed and cannot be changed after the serial loop codelet's construction. If a more dynamic approach is required, one can pass a reference to a variable rather than a static value. This is useful if data required by the loop body is not known when the loop controlling codelet is created. The following shows an example of a serial loop. The loop CDG requires an addition integer, Number. Notice how this affects the constructors of the loop and serial for.

```

#include <iostream>

```

```

2 #include ''darts.h''

```

3 using namespace darts;

```

4

class FormalLoop : public Loop

{

6

public:

7

int number;

8

HelloCodelet hello;

9

GoodByeCodelet goodbye;

10

11

FormalLoop(unsigned int Id, Codelet * ToSignal, int Number):

12

loop(Id, ToSignal),

13

number(Number),

14

hello(0, 0, this, 0),

15

goodbye(1, 1, this, 0)

16

{

add(&hi);

18

}

19

};

20

21

class TPwithSerialLoop : public ThreadedProcedure

22

{

23

public:

24

serialFor<FormalLoop> serialLoop;

25

26

TPwithSerialLoop(Codelet * ToSigal, int Iterations, int Number):

serialLoop(0, 0, this, 0, ToSignal, Iterations, Number),

28

{

29

add(&serialFor);

30

}

31

};

32

```

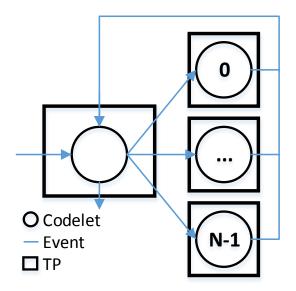

# 4.1.3.2 Codelet For All Loop

A codelet for all loop differs from a serial codelet loop as its iterations may execute in parallel within a single cluster. The codelet loop has a nearly identical form to the serial loop (except the name of the object) requiring the same parameters, template parameters, and parameter order. The differences between the codelet loop and the serial loop are evident during their respective construction (which is invisible to the application programmer). The codelet loop codelet allocates a separate loop CDG for each iteration upon creation. Each iteration is constructed with a unique iteration id (ranging from zero to the total number of iterations minus one) and a reference to the codelet loop codelet. The arguments required by the loop CDGs are passed by the runtime to the loop constructor. The codelets from all of the iterations may run in parallel within the same cluster. As each iteration finishes, the codelet loop codelet is signaled. Once all of the iterations are complete, the codelet loop codelet signals the next codelet provided during construction. The following is an example of a codelet for all loop.

Figure 4.1: A codelet for loop spawns N loop iterations (one codelet per iteration in this figure). These iterations are all executed in a single cluster. Upon completion, the iterations signal the codelet that initiated the loops which continues execution.

<sup>#</sup>include <iostream>

```

#include ''darts.h''

2

using namespace darts;

3

4

class SemiInformalLoop : public Loop

5

{

6

public:

7

int number;

8

HiCodelet hi;

9

ByeCodelet bye;

10

11

SemiInformalLoop(unsigned int Id, Codelet * ToSignal, int Number):

12

loop(Id, ToSignal),

13

number(Number),

14

hi(0, 0, this, 0),

bye(1, 1, this, 0)

16

{

17

add(&hi);

18

}

19

};

20

21

class TPWithCodeletLoop : public ThreadedProcedure

22

{

23

public:

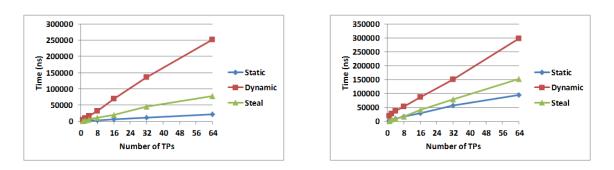

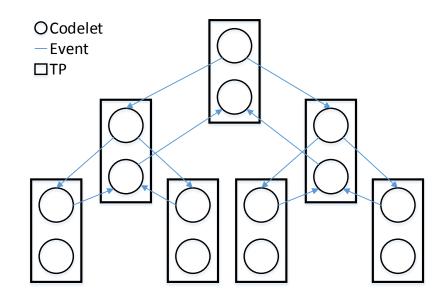

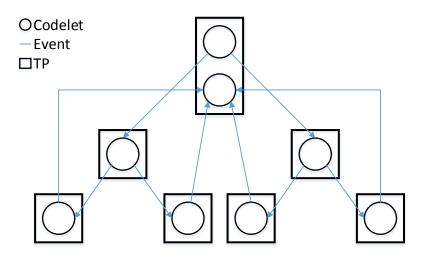

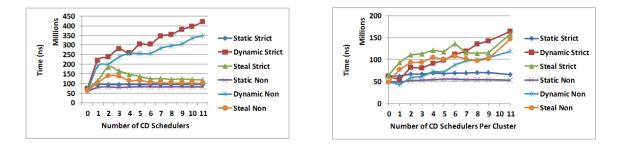

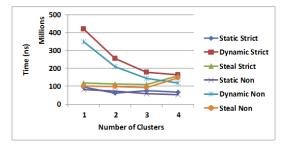

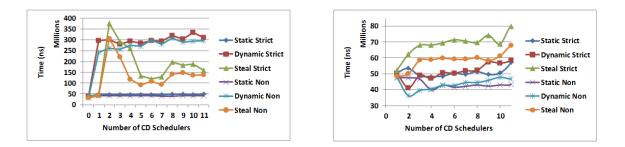

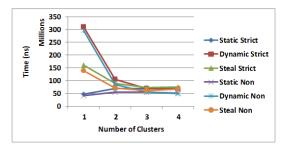

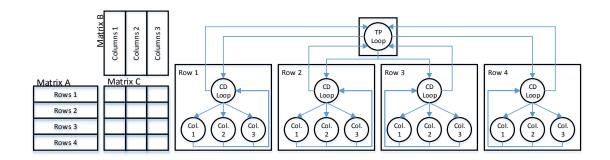

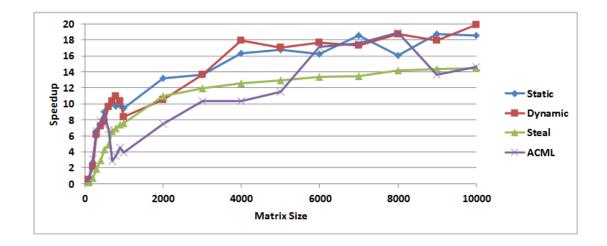

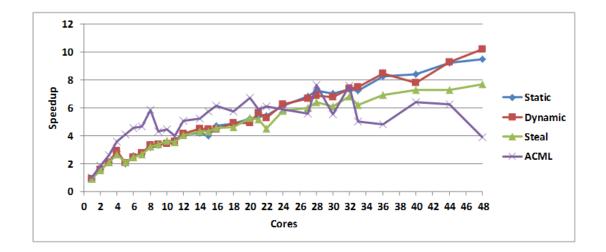

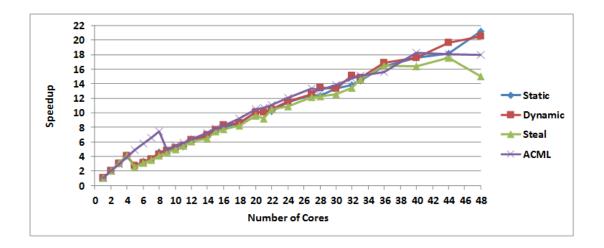

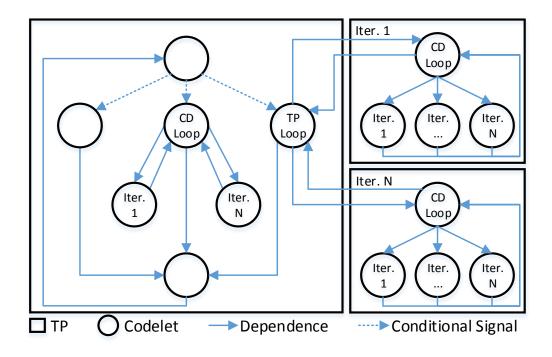

24